Foreword

At present, many users use the 16MHz internal oscillation or external crystal as the clock source when using the STM8. In fact, some families in the STM8 family support up to 24MHz frequency, such as STM8S207, STM8AF52, and so on. So, when faster speeds are needed, can you just run with a higher clock speed?

problem

A customer used the STM8AF52A9 in the design of their products. The customer engineer stated that it had previously verified a code that could not function properly after downloading using STVP. But he tried to debug it normally in IAR for STM8. I don't know why it wouldn't work after I used STVP.

Research

1. Understand the problem

Using the compiled .s19 file to write to the STM8AF52A9 using STVP, it was found that it was not working after power-up. Observe the user code and enter the debugging state in the IAR. You can debug breakpoints and single-step debugging. However, when it was finally found that during online debugging, the program died when it reached the following code.

Status = CLK_ClockSwitchConfig(CLK_SWITCHMODE_AUTO, CLK_SOURCE_HSE, DISABLE, CLK_CURRENTCLOCKSTATE_DISABLE);

2. Analyze the problem

After the STM8 is powered on, the default primary clock source is the internal HSI RC clock divided by 8, ie fHSI/8. The reason is that the stabilization time of the HSI clock is short, and the 8 division ensures that the system starts safely under poor VDD conditions. After the primary clock source is stable, the user can switch the master clock to another clock source.

Let's look at the prototype of this function just now:

ErrorStatus CLK_ClockSwitchConfig(CLK_SwitchMode_TypeDef CLK_SwitchMode, CLK_Source_TypeDef CLK_NewClock, FunctionalState ITState, CLK_CurrentClockState_TypeDefCLK_CurrentClockState)

Its role is to switch the clock source. CLK_SwitchMode represents the switching mode used, automatic switching and manual switching; CLK_NewClock represents a new clock source; ITState represents whether the interrupt is enabled or disabled; CLK_CurrentClockState represents whether the state of the original clock source after switching is maintained or closed. Therefore, the meaning of the user code is: using the automatic switching mode, switching the master clock to the HSE does not generate an interrupt, and the original master clock source is switched off after switching.

After switching the main clock source, the program will have a problem. It seems that the problem is likely to be in the HSE. The external crystal must be detected. It was originally thought whether there was any problem with the oscillation of the external crystal of the HSE, but after using the oscilloscope to detect it, it was found that the HSE was already in the normal oscillation, and the waveform was very beautiful. However, on the oscilloscope, the frequency is 24MHz. Check the mark on the crystal, it really is 24MHz frequency. Therefore, when customers use STM8AF52A9, in order to improve performance, the highest frequency 24MHz is used.

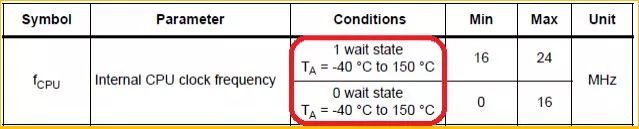

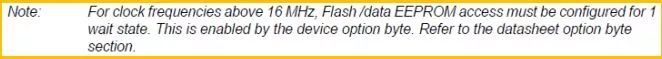

The customer's problem should be in the use of 24MHz. Customers used 16MHz clock frequency before. STM8 requires that if the master clock frequency used by the user exceeds 16 MHz, then the flash and EEPROM accesses need to be configured for a wait period.

The STM8AF52A9 data sheet can be seen as follows:

Reference Manual RM0016 In the description of HSE, also mentioned:

For selecting 0 wait period or 1 wait period, you must select in the option byte. Check the chip's option byte and find that the selected 0 wait period, so the problem lies in this.

3. Problem solving

Using STVP, modify the option byte on the OPTION BYTE page and set the wait period to 1 wait period, as follows:

Downloading the chip's option byte, using the previous .hex file, works fine.

in conclusion

Since the 24MHz main frequency used has exceeded 16MHz, and the wait period is not changed in the option byte is a waiting period, there is a problem in the Flash access and the program cannot be normally operated.

deal with

The option byte needs to be modified to change the wait period to 1 wait period.

Description of Stacked D-Sub I/O Connectors

Antenk's connectors are designed for applications requiring multiple connector ports with limited PCB space

The condensed footprint of Antenk's dual port D-sub solution is available in four industry sizes, three connector spacing options, and six hardware configurations for one of the broadest stacked D-sub offerings on the market in standard and high-density variations.

Stacked D-sub I/O connectors are designed for applications requiring multiple connector ports with limited PCB space. Two right angle D-sub connectors are stacked one on top of another, creating a single dual-port connector with a very condensed footprint.

Features of Stacked D-Sub I/O Connectors

Available in four industry standard sizes:

Standard density: 9, 15, 25, 37

Available in three connector spacing options: 0.625", 0.750", 0.900"

Available in six hardware configurations

High-temperature UL94 V-0 thermoplastic (260°C process temp)

High performance stamped contacts

Applications of Stacked D-Sub I/O Connectors

Communications

Instrumentation

Medical

Computers/peripherals

Commercial industry

Test labs

Gaming industry

Range of of Stacked D-Sub I/O Connectors

Male Stacked D sub Connector

Female Stacked D sub ConnectorStandard Density Stacked D sub Connector

High Density Stacked D sub Connector

Dual-Port Stacked D-Sub Connectors

Dual Port (Stacked) D Sub,,Stacked D Sub I/O Connectors,Dual-Port Stacked D-Sub Connectors,Male Stacked D sub Connector, Female Stacked D sub Connector, Standard Stacked D sub Connector, High Density Stacked D sub Connector

ShenZhen Antenk Electronics Co,Ltd , https://www.antenkcon.com