Three design patterns

1. Plane mode

The first mode is the Planar Pattern, which derives from the "control plane" and "data plane" that divide the processing tasks of a communication system. It is an extensive and different type of multi-core design example, this multi-core design is collectively referred to as asymmetric multi-processing technology (abbreviated as "AMP" or "ASMP").

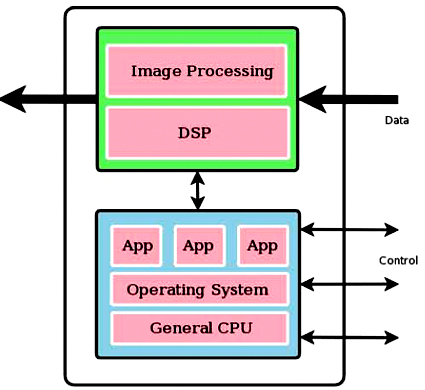

Figure 1: Planar mode for image processing

If planar mode is used, the system needs to be divided into multiple self-contained modules with significantly different processing requirements. In its standard form of communication and media processing, this model has the advantage of running algorithms that require extensive data processing on a dedicated DSP or network processor while maintaining the normal operation of other system software on a common CPU. This particularity means that the planar mode system is usually implemented on specialized component hardware. Because many planar hardware devices have only one general-purpose CPU core, traditional single-core tools, operating systems, and design methods can be used to design and debug common parts of the system.

2. On-grid pattern

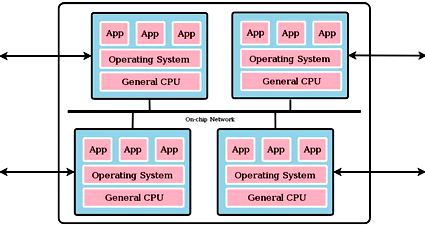

The Grid-on-Chip (or Grid for short) mode is a deduction of the planar mode, including any multi-processor system composed of many completely independent and interconnected nodes. A grid is an on-chip version of an office computer network. It is a number of network processing nodes that share adjacent physical links but are independent of each other. Some literature refers to this type of system as a distributed multi-processing system and still categorizes it into the general category of AMP/ASMP systems.

The key requirement for using the grid pattern is to first partition the system and then find a suitable internode communication system. (Although more advanced grid systems can reconfigure themselves during operation, the designers of raster mode systems need to think carefully about the allocation of system functions to processing nodes.) In addition to partitioning, a grid system has three The least advanced design constraints in a design pattern. Once the system is partitioned, the design and implementation of each individual node will behave as an independent system. The grid system can be implemented on dedicated hardware, but another common choice is to create grid nodes by employing SMP hardware and dividing the shared memory space into segments for each core.

Grid mode systems have several outstanding advantages over other designs. First, they can be easily integrated with past software, and past systems can even continue to run completely on their own nodes in the grid. In addition, grid systems have significant advantages in terms of determinism and debugging capabilities. The loose coupling of the grid-mode system design means that there will not be much surprises in terms of resource competition. Because familiar single-core debugging methods can be used for each isolated system node, debugging is relatively simple. The divisional nature of the raster-mode system makes it more powerful, but it is also at the root of its flaws, because segmentation makes it difficult to redistribute resources, which will cause the grid system to lack flexibility in adapting to future and unforeseen requirements. .

Figure 2: Grid Mode System

3. SMP mode

In a symmetric multiprocessing (SMP) system, a single-image operating system is the top layer of a processing core running on two or more shared memory spaces. These processor cores are essentially the same. Just like a multi-core desktop computer, an SMP mode system can dynamically balance tasks on a group of processor cores. This ability to redistribute processing power to match current tasks is a major advantage of SMP systems, which also makes SMP systems the most flexible and adaptable of the three modes. With today's SMP real-time operating system, this flexibility eliminates the need for decision or real-time response at the expense of any performance.

Figure 3: SMP System Example

An SMP mode system requires two conditions: one is a symmetric shared memory multi-core processor platform, and the other is an SMP-capable operating system. Many of today's processor families support SMP functionality, and there are multiple channels available for SMP operating systems. Two of the more prominent advantages of SMP systems are that developers are more familiar and can start quickly. In theory, developers can easily start an operating system with SMP capabilities and port existing application designs. Developers can quickly take advantage of multi-core hardware performance.

The reality is basically the same, but there are several issues that need to be kept in mind. The first issue worth paying attention to is the hard real-time requirement. A real-time operating system (RTOS) that supports SMP functions will not sacrifice real-time performance. However, when SMP is used, operating systems that do not have hard real-time capabilities will lack decision-making features. And lack of more advanced and more variable interrupt response time. There is no need to worry about this for a good SMP RTOS, but keep in mind that a generic operating system may perform differently on SMP hardware than it does on a single-processor system.

The second potential issue is resource competition. A prominent advantage of SMP systems is that many resources are shared, which makes the SMP system more flexible and adaptable. However, this advantage is also a disadvantage. Since all resources are shared, unpredictable performance changes due to resource competition will occur. This will not happen in every system, but if developers want the system to run at its designed performance, it is still important to keep this in mind.

Design and debugging

Just like the embedded development, in the hardware design process, it is necessary to first consider the development and debugging of the software. Ensuring that the design has on-chip debugging (OCD) capabilities will greatly speed up the system development process and provide a reliable tool for programming and analysis systems. In the flat design mode and grid design mode, a single OCD port allows developers to debug a single kernel of the system as if they had a more traditional single-core system.

The real-time trace port is another debugging feature that becomes more and more important as the number of cores in the system continues to grow. Real-time tracking provides a standard way to observe the interactions between the cores without breaking the sensitive timing that is critical to the reproduction problem. This will make system development easier if the multi-core device contains one or more real-time trace ports.

There is an often-mentioned but not realistic statement: Although many developers have successfully adopted these three design patterns, software development tools are not designed for multi-core applications. Now, there is already a real-time operating system that supports SMP functionality, and can provide developers with a flexible SMP mode that does not waste real-time decisions. For designs using planar and grid modes, developers can take advantage of existing familiar, proven single-core design tools and methods. Multi-core design can make the system more complex, but the tools and methods that have been developed can help developers manage the complexity of multi-core hardware, achieve its powerful features, and cost.

LED street lights achieve ultra brightness/luminance; energy-saving over 70%. Special modular design for theLens (independent modules) and high luminous efficacy, high CRI, easy for maintenance.Intelligent and isolated power supply (NS semiconductor and Japan Rubycon capacitor), reliable and stable; automatically reduce current against overheating working temperature

Led Street Light,Street Lamp,Led Lamp,Street Lamp Post

Yangzhou Beyond Solar Energy Co.,Ltd. , https://www.ckbsolar.com