Current control methods in industrial control systems: The underlying equipment uses the RS232 bus architecture, and the upper management layer generally adopts the Ethernet structure. This control method enables signals to be published and shared on the company's intranet in a timely manner. Online control, function configuration, and remote diagnosis of on-site smart devices can also be performed anywhere on the Internet/Intranet, realizing the true openness of control networks. Sex and interoperability. The RS485 bus is a serial bus based on balanced transmission and differential reception. It has a strong resistance to common-mode interference and the transmission distance is very long at the proper baud rate. At the same time, due to its simple hardware design, convenient control, and easy network expansion, it is widely used in many industrial sites.

The embedded Ethernet adapter studied in this paper is to solve the problem of embedded device network communication, facilitate the communication between the embedded system and the computer network, and achieve remote monitoring, access, and data transmission.

First, the main chip selection and introduction1, microcontroller AT89S52

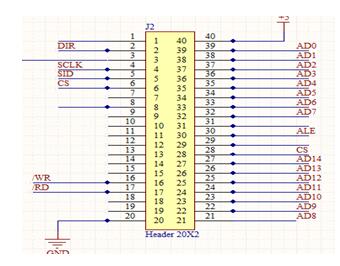

AT89S52 is designed as the core processor in this design. The AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller manufactured by Atmel Corporation. The chip contains 8k bytes of EPROM and 256 bytes of RAM. With ISP (in-system programming) function. It has the advantages of high flexibility, ease of use, and low price. Therefore, the chip has been widely used in embedded control systems. Microcontroller AT89S52 is transmitted to the PC via Ethernet for remote control. Using the AT89S52's ISP (in-system programming) function, it is easy to write programmed programs into the microcontroller and it is easy to debug, modify, and upgrade. Since AT89S52 microcontroller itself provides a set of full-duplex serial transmission port, TXD pin to transmit serial data, and RXD pin to receive data, but its working logic level is TTL level (0V, 5V ). The AT89S52 minimum system is shown in Figure 1.

Figure 1 AT89S52 minimum system

2, network control chip ENC624J600

The ENC624J600 network controller is a standalone Ethernet control chip designed for embedded applications with an industry-standard serial interface and parallel interface. The ENC624J600 communicates with the microcontroller through an SPI or parallel interface. The data transfer rate is 14 Mbit/s (for SPI) to 160 Mbit/s (for a 16-bit parallel interface). The main features of the ENC624J600 are adaptive selection of the transfer rate, supporting 10 Mbit/s. s or 100Mbit/s; full support for half-duplex or full-duplex switched Ethernet; programmable fill and CRC generation; 24KBA on-chip RAM buffer for performing send and takeover operations, the host microcontroller can also use it Perform regular storage operations; support bus 8-bit or 16-bit CPU access, programmable automatic rejection of error packets; programmable for automatic retransmission when a conflict occurs.

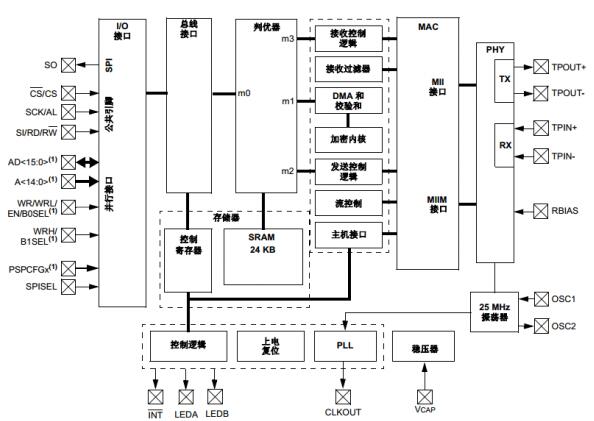

The ENC624J600 device complies with all IEEE 802.3 specifications for 10 Base-T and 100 Base-TX Ethernet, including many optional terms such as auto-negotiation. The ENC624J600 device employs a series of packet filtering mechanisms to limit incoming data packets. It also provides a 16-bit wide internal DMA for fast data throughput and hardware IP checksum calculation support. A secure engine module is provided for applications that require the security and authentication capabilities of SSL, TLS, and other encryption-related protocols. The engine can perform RSA, Diffie-Hellman, AES, MD5, and SHA-1 algorithmic calculations to reduce code size, speed connection setup and throughput, and reduce firmware development effort. Communicating with the microcontroller via the SPI or parallel interface, the data rate is 14 Mbit/s (for SPI) to 160 Mbit/s (for 16-bit demultiplexed parallel interfaces). Provides pins dedicated to LED connections, activity indication, and transmit/receive/DMA interrupts. A general purpose 24 KB on-chip RAM buffer is provided for performing transmit and receive operations. The main microcontroller can also use it for regular memory operations. Communication protocols such as TCP can use this memory to hold data that may need to be resent. Each device of the ENC624J600 series is pre-programmed with a unique non-volatile MAC address in terms of ease of production of the final product. In most cases, this saves the final device from serial programming steps. Figure 2 shows the general block diagram of the device.

Figure 2 Block diagram of the ENC624J600

3, external data memory FM1808

FM1808 is based on the principle of ferroelectric memory manufacturing parallel interface 256Kbit ferroelectric memory, FM1808's main features are as follows: the use of advanced ferroelectric technology; storage capacity of 256Kbit; read and write life of 10 billion; power-down data can be saved for 10 years Write data without delay; access time is 70ns; low power consumption, working current is 25mA, standby current is only 20uA; single 5V working voltage is used; operating temperature range is -40°C~+85°C; Resistant to moisture, shock and shock; compatible with SRAM or parallel EEPROM pins.

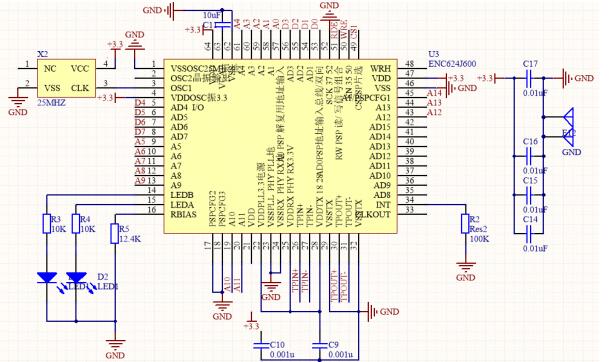

Second, the hardware circuit design1. Design of connection circuit between AT89S52 and Ethernet controller

In this system, port P0 is used as the lower 8-bit address/data multiplex and is used as the data line to connect the 8-bit data interface of the NC624J600. When used as an address line, in order to provide the ENC624J600 with the lower 8 bits of a 15-bit address, multiplexing techniques are used to separate the address from the data. Therefore, P0 port is connected to D0~D7 of 74ls373, and the lower 8-bit address is temporarily stored. O0~O7 of the address latch are then provided to the ENC624J600 to provide the lower 8 bits of the 15-bit address, and the upper 7 bits are provided by the P2 port through 74ls245. ,As shown in Figure 3.

To make the interface with the microcontroller highly flexible, the ENC624J600 device offers two options: a Serial Peripheral Interface (SPI)-based serial interface and a flexible 8/16-bit parallel slave port interface. Only one interface can be used at any given time. In this topic, the connection between the AT89S52 microcontroller and the ENC624J600 selects the PSP interface, as shown in Figure 3. To select the PSP interface, the I/O interface is hardware selected by the SPISEL function on the INT/SPISEL pins at power-up. To complete this operation, the level applied to this pin must be latched for approximately 1 to 10 μs after powering the device and exiting the power-on reset state. If SPISEL is latched at a logic high state, the serial interface will be enabled. If the SPISEL is latched at a logic low state, the PSP interface is enabled.

Fig. 3 The design of connecting circuit of AT89S52 and Ethernet controller

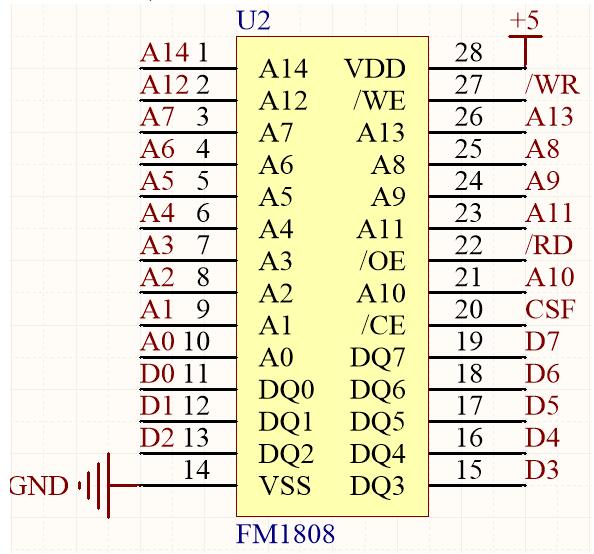

2. Circuit design of AT89S52 and external expansion memory FM1808

The connection between AT89S52 and FM1808 is similar to the connection between AT89S52 and NC624J600. Port 0 is multiplexed as lower 8-bit address/data and used as data line to connect 8-bit data of FM1808. When used as an address line, a multiplexing technique is used to separate the address from the data. The FM1808 is provided with the lower 8 bits of the 15-bit address, and the upper 7 bits are provided by the P2 port through 74ls245, as shown in FIG.

Figure 4 Circuit design of AT89S52 and external expansion memory FM1808

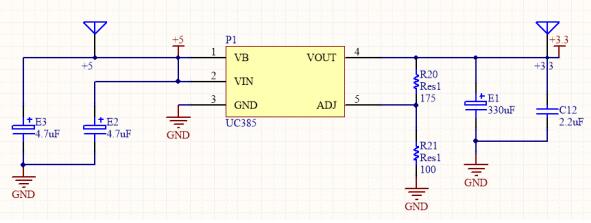

3, power circuit design

The power supply module is the most basic part of a circuit board. Only the stable and reliable power supply can supply power to the on-board chip to ensure the normal operation of each functional module. Therefore, when designing the power supply module, the power consumption of all components of the circuit board should be initially calculated. , and then under the premise of ensuring power consumption, select the appropriate chip for DC power module design, as far as possible to achieve a small size, light weight; reasonable price; can work long-term stable and reliable.

The adapter requires 3.3V of power. The system requires a 3.3V power supply chip Ethernet controller. Considering that the system may work in high-speed communication mode, the consumption current will be very large. Therefore, one UC385 chip is selected, and each UC385 output current can reach 800mA, which can fully meet the needs of the system. The specific circuit is shown in Figure 5.

Figure 5 Power Module Design

Third, the software design1, the main function

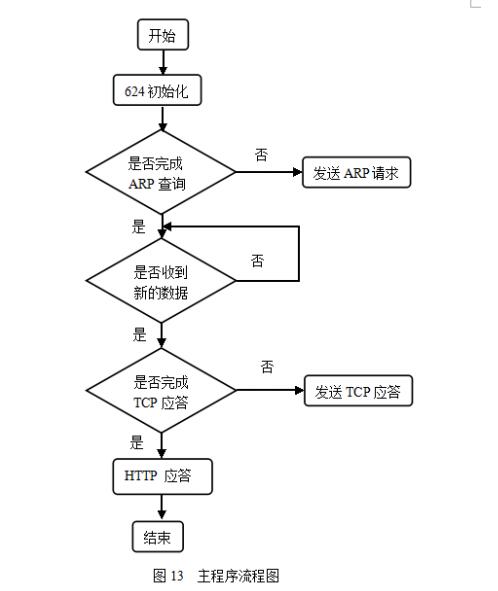

The ARP is first queried when powered on, and the ARP request is sent if no MAC is obtained. If there is new data, if the TCP response is not completed, the TCP is answered and the TCP three-way handshake is completed. Then respond to HTTP based on the request type.

2, TCP response part

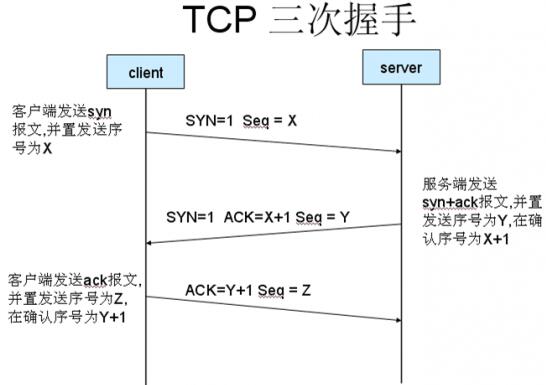

1) Three-way handshake

The so-called three-way handshake (Three-way Handshake), refers to the establishment of a TCP connection, the client and the server need to send a total of 3 packets. The purpose of the three-way handshake is to connect to the specified port of the server, establish a TCP connection, and synchronize the serial number and acknowledgment number of both sides of the connection and exchange the TCP window size information.

Figure 6 Three-way Handshake

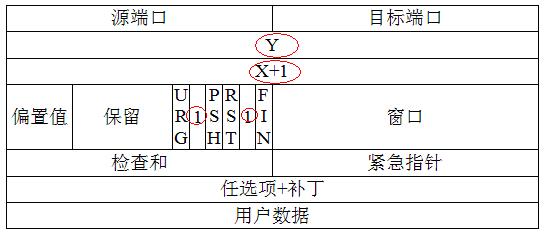

First handshake: The client sends a TCP packet with the SYN flag bit set to indicate the port of the server to which the client intends to connect, and the initial sequence number X, stored in the Sequence Number field of the packet header.

Figure 7 The first handshake

Second handshake: The server sends back an acknowledgement (ACK) reply. That is, both the SYN flag and the ACK flag are 1 and the Acknowledgement Number is set to the customer's ISN plus one. That is X+1.

In the third handshake, the client sends an acknowledgment packet (ACK) with the SYN flag set to 0, the ACK flag set to 1, and the server sends the ACK sequence number field +1 and sends it to the other party in the definite field. And write ISN +1 in the data segment

Figure 9 The third handshake

In fact, when the handshake and the end of the confirmation number should be the other party's serial number plus 1, the transmission of data is the other party's serial number plus the other party to carry the application layer data length.

In the process of transmitting the TCP packet, it is also necessary to send a packet to confirm a packet, and the TCP packet only has 54 bytes, that is, only the header information. Therefore, the serial number of the TCP packet is not changed during transmission, and the confirmation number is incremented according to the length of the transmitted data.

3, HTTP

1) Request

After the connection is successfully established, it begins to send a request to the web server. This request is generally a GET or POST command (POST is used to pass FORM parameters). The format of the GET command is: GET path/filename HTTP/1.0 file name indicates the file accessed, and HTTP/1.0 indicates the HTTP version used by the web browser. You can now send a GET command: GET /mytest/index.html HTTP/1.0,

2) Answer

The web server receives this request and processes it. Search the file index.html in the subdirectory mytest from its document space. If the file is found, the web server passes the contents of the file to the corresponding web browser. In order to inform the browser, the Web server first transmits some HTTP header information, and then transmits the specific content (ie HTTP body information). The HTTP header information and the HTTP body information are separated by a blank line. Common HTTP header information includes:

1 HTTP 1.0 200 OK This is the first line of the web server reply, listing the HTTP version number and reply code that the server is running. The code "200 OK" indicates that the request is completed.

2 MIME_Version:1.0 This indicates the version of the MIME type.

3 content_type: type This header information is very important, it indicates the MIME type of HTTP body information. For example: content_type:text/html indicates that the data transferred is an HTML document.

4 content_length: Length value It indicates the length (in bytes) of the HTTP body information.

3) Close the connection

After the response is over, the web browser and web server must be disconnected to ensure that other web browsers can establish a connection with the web server.

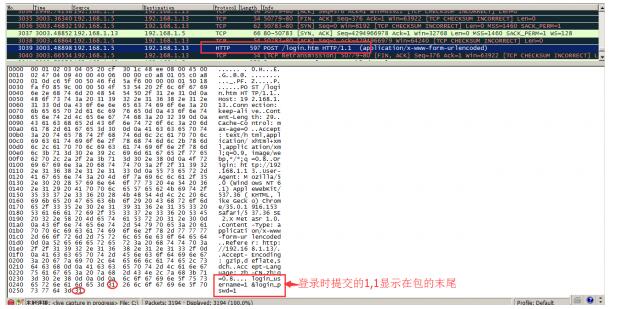

4, submit the form GET / POST

The data of the GET request is appended to the URL (that is, the data is placed in the header of the HTTP protocol). Divide the URL and transfer the data, the parameters are connected with &, for example: login.acTIon? Name=hyddd&password=idontknow&verify=%E4%BD%A0%E5%A5%BD. If the data is an English alphabet/number, it is sent as is. If it is a space, it will be converted to +. If it is a Chinese/other character, the string will be encrypted with BASE64, and the result is: %E4%BD%A0%E5%A5% BD, where XX in %XX is ASCII in hexadecimal notation for this symbol.

POST places the submitted data in the body of the HTTP packet. In FORM (form), Method defaults to "GET".

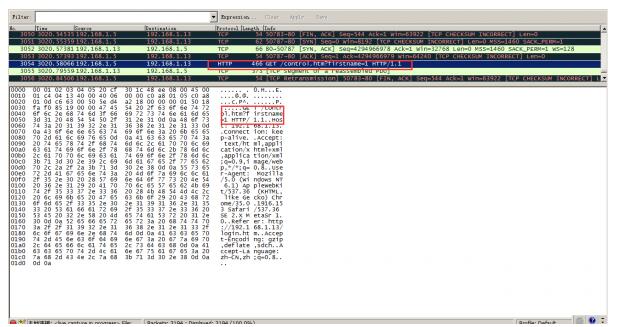

In this article, when submitting form data, the POST method is used, and the control information form is submitted using GET. The following is a clear picture of the difference between them by using a packet capture method.

Figure 10 POST mode

Figure 11 GET method

Figure 12 GET method is to submit the data directly in the URL

5, overall software design

The AT89S52 microcontroller first initializes the ENC624J600. First, it should query the CLKRDY bit of the ESTAT register to ensure sufficient delay before configuring the MAC and PHY registers. The PHY register is used to set the communication mode; the ERXST and ERXND pointers are programmed to initialize the receive buffer. When programming an ERXST pointer, the same value will automatically update the ERXWRPT register. The receiving hardware will write the received data from the address in the ERXWRPT. To track the received data, the ERXRDPT register also needs to be programmed with the same value; To minimize the main controller's processing workload, the ENC624J600 is equipped with different filters that automatically reject unneeded packets. All filters are configured by the ERXFCON register, and several filters can be used with the ANDOR bit pair. The test results are logical/zero or logical and/or zero operations; since the memory space not used as a receive buffer acts as a transmit buffer, no special initialization of the transmit buffer is required, and the memory space is usually allocated as Large receive buffer space and smaller receive storage space.

After the initialization is completed, that is, enter the main loop program, the microcontroller will repeatedly detect whether the ENC624J600 receives an Ethernet frame (or data in the data buffer B need to send), when there is data received (or sent), according to the flag bit corresponding The sub-function processing, the data is stored in the data buffer (or sent to the Ethernet). The main program flow is shown in Figure 13.

The utility model discloses an Electronic Cigarette with atomizer oil core separation structure, which comprises a atomizer assembly and a battery assembly; The utility model has the advantages of reasonable structure design and high practicability. During operation, because the oil storage tank of the atomizer is completely sealed and the oil guide material is completely isolated from the oil guide material, the oil guide material will never contact with the oil guide material in the storage process

Advantages:

Oil core separation, Mesh removable heating core, Ultra quiet design,100% oil leakage free, Excellent taste, Cost far less than the industry price.

A variety of colors and finishing are available, can be adjusted according to your market needs.

Oil Coil Separation Pod Patent,Oil Coil Separetion Vape Pod Oem,Innovated Vape Products Oem,Oil Coil Separation Vape Products Oem

Shenzhen MASON VAP Technology Co., Ltd. , https://www.disposablevapepenfactory.com