When wiring congestion occurs in the design, it usually leads to increased wiring delay, which affects timing closure. The degree of wiring congestion can be obtained in the following two ways:

-The level of congestion will be displayed in the log file of the wiring phase

-For the dcp file generated by place_design or route_design, you can get it through the following command

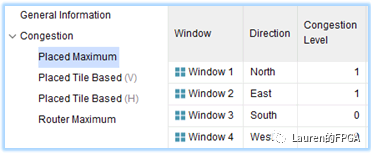

The generated congestion report is shown in the figure below. Pay special attention to areas where the congestion level is greater than 4.

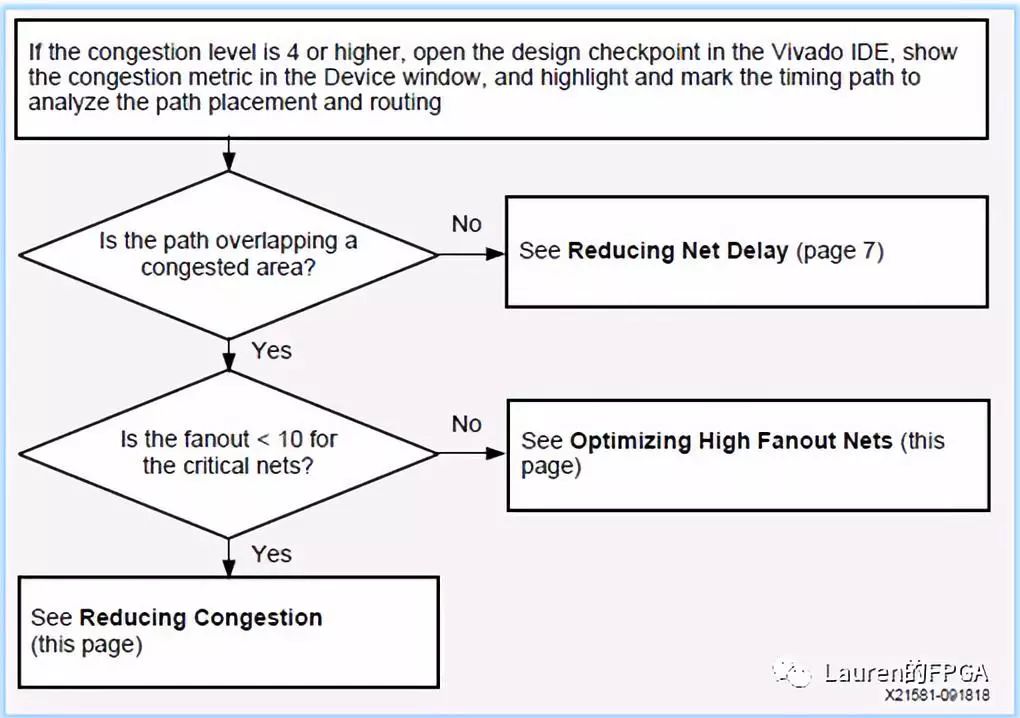

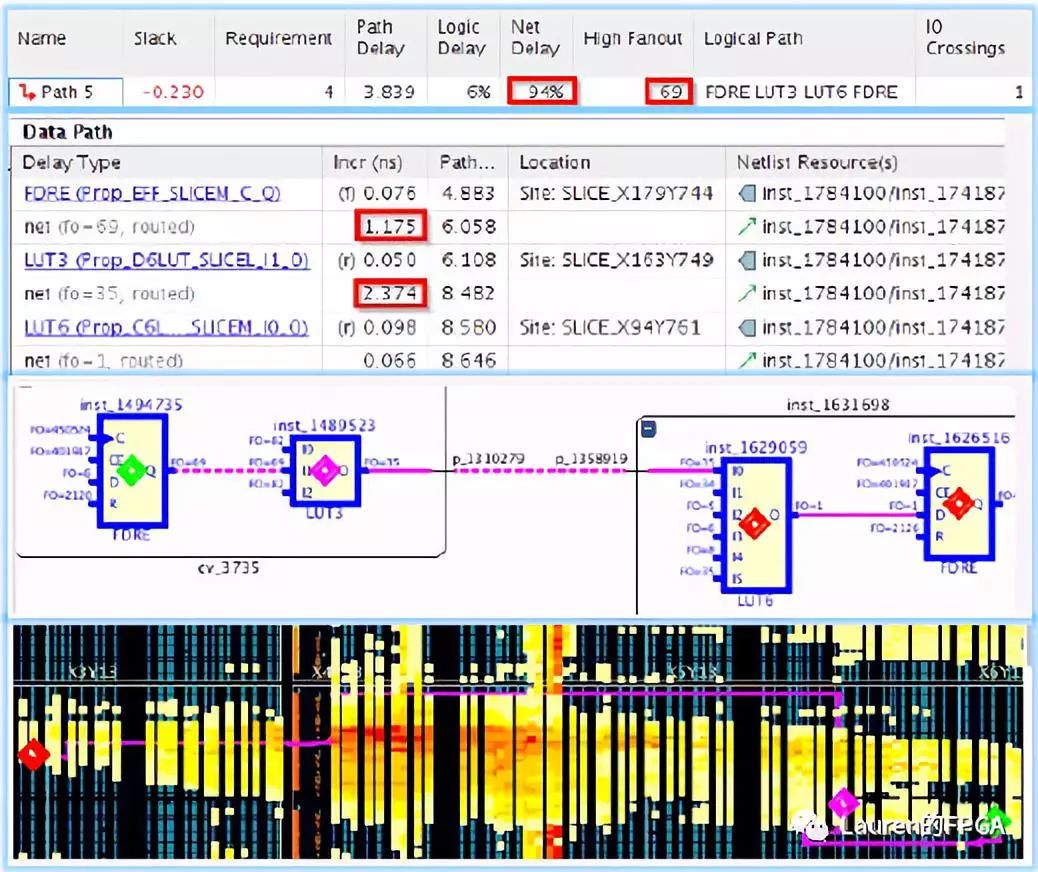

For situations where the congestion level is greater than 4, the following process can be used to improve and reduce wiring delay. In the following case, you can see that the wiring delay accounts for 94% of the total delay. Based on this, it can be concluded that the wiring delay is the root cause of the timing violation. Judging from the wiring results, a winding appeared in the congested area.

Image source: page 6, ug1292

Image source: page 6, ug1292

Reducing congestion can improve cabling quality. Xilinx recommends the following methods to improve wiring congestion.

(1) When the overall resource utilization rate reaches 70% to 80% (for multi-die chips, this value refers to the resource utilization rate of each SLR), some modules need to be cut to reduce the resource utilization rate. In particular, it is necessary to avoid the situation where the utilization rate of LUT/BRAM/DSP/URAM is greater than 80% at the same time. If the utilization rate of these blocks of BRAM/DSP/URAM cannot be reduced, ensure that the utilization rate of the LUT is less than 60%.

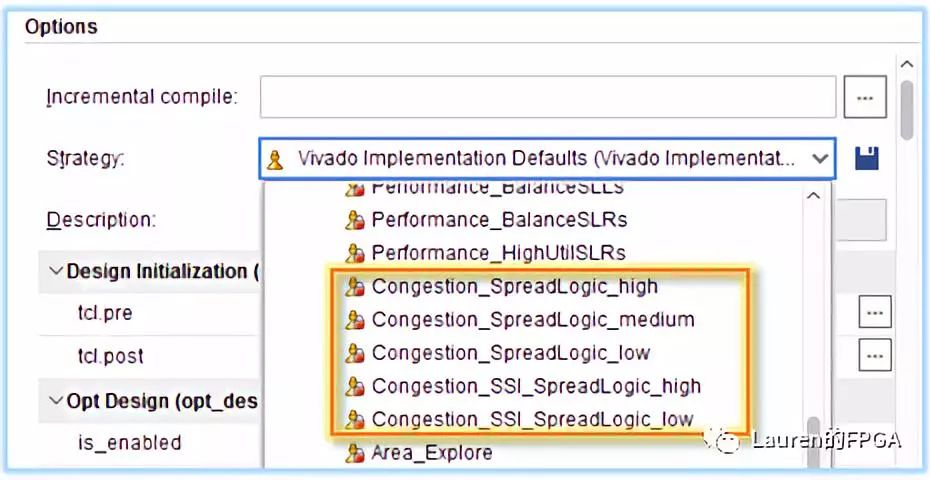

(2) When executing place_design, try to set -directive to AltSpreadLogic* or SSI_Spread* or set the Strategy of Implementation to Congestion_*, as shown in the figure below.

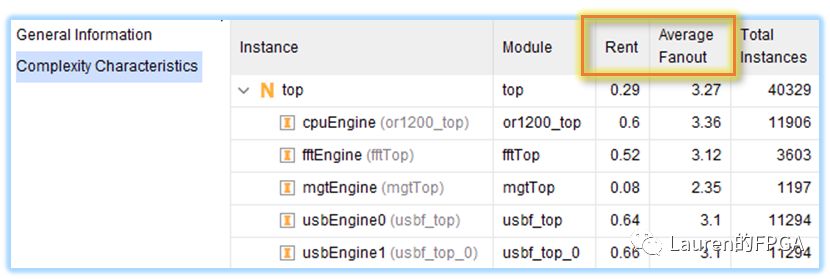

(3) Analyze the design complexity through the following commands and find the congested modules in the design (Rent value greater than 0.65 or AverageFanout greater than 4). Afterwards, implement modular synthesis for these modules, and the comprehensive strategy is set to ALTERNATE_ROUTABILITY.

Generate design complexity report:

Adopt modular integrated technology for congestion module:

(4) Reduce the utilization rate of MUXF* and LUT-Combining in the congested area. The specific method can sometimes be obtained through report_qor_suggestions. But the use of modular integrated technology is a method worth trying.

(5) The introduction of BUFG on the non-critical high fan-out cable in the wiring area can be achieved through the following commands.

(6) Inherit the layout of DSP/BRAM/URAM from the previous low-congestion wiring or layout results. This can be achieved by the following script.

Optimize the high fan-out network cable:

(1) At the RTL level, copy registers based on the design level to reduce fanout, or reduce fanout through the -hier_fanout_limit option in the opt_design phase.

(2) In the phys_opt_design (post-layout) phase, use -force_replication_on_nets to reduce the fan-out of the key high fan-out network cable by copying the register.

Insulation Silicone Rubber Fiberglass Sleeve

Insulation Silicone Rubber Fiberglass Sleeve,Insulation Fiberglass Insulation Sleeve,Insulation High Temp Fiberglass Sleeving,Insultherm Fiberglass Braided Sleeving

Longkou Libo Insulating Material Co.,Ltd. , https://www.sdliboinsulation.com