â— Large capacity 2048 bytes of on-chip RAM data memory

â—High speed: 1 clock/machine cycle, enhanced 8051 core (STC Y5), 7-12 times faster than traditional 8051

Speed ​​is also 20% faster than STC's early 1T series microcontrollers (such as the STC12/11/10 series)

â— Wide voltage: 5.5 to 3.8V, 2.4 to 3.6V (STC15L2K60S2 series)

â— Low-power design: low-speed mode, idle mode, power-down mode (can be awakened by external interrupt or internal power-down wake-up timer)

Internal high-precision R/C clock, ±1% temperature drift (-40°C~+85°C), 5 Hz at normal temperature, completely eliminating the expensive external crystal clock, internal clock from 5MHz~35MHz

â— Internal high-reliability reset, 8-level reset threshold voltage is optional during ISP programming, completely eliminating external reset circuit

â— Resources that support power-down wake-up include: INT0/INT1 (rising edge/falling edge interrupt), -INT2/-INT3/-INT4 (falling edge interrupt); CCP0/CCP1/CCP2/RxD/RxD2/T0/T1 /T2 pin; internal power-down wake-up timer

â— Operating frequency: 5 ~ 35MHz, equivalent to ordinary 8051: 60 ~ 420MHz

â— 8/16/24/32/40/48/56/60/61K bytes of on-chip Flash program memory, more than 100,000 erase and write times

â— Large-capacity on-chip EEPROM (FLASH) function, more than 100,000 times of erasing

â— ISP / IAP (programmable in the system / programmable in the application), no programmer / emulator required

â— High-speed ADC, 8-channel 10-bit, speed up to 300,000 times / sec. 3-way PWM can also be used as 3-way D/A

â— 3-channel capture/compare unit (CCP/PCA/PWM)

---- Can also be used to implement 3 D/A 3 timers or 3 external interrupts (support rising edge / falling edge interrupt)

â— 6 timers, 2 16-bit reloadable timers T0 and T1 are compatible with ordinary 8051 timers, a 16-bit timer T2 is added, and clock output can be realized. 3 CCP/PCA can be realized again. 3 timers

â— Programmable clock output function (clock-divided output of internal system clock or external pin clock input):

1 T0 outputs the clock at P3.5;

2 T1 outputs the clock at P3.4;

3 T2 is output clock at P3.0, and the above three timer/counter output clocks can be divided by 1~65536.

4 The internal main clock is output to the external clock of P5.4/MCLKO (the main clock of STC15 series 8-pin MCU is output clock of P3.4/MCLKO)

â— Hardware Watchdog (WDT)

â—SPI high-speed synchronous serial communication interface

â— Dual serial port / UART, two completely independent high-speed asynchronous serial communication ports, time-sharing can be used as 5 serial ports

â— Advanced instruction set structure, compatible with ordinary 8051 instruction set, with hardware multiplication/division instructions

â— General-purpose I/O port (42/38/30/26), after reset: quasi-bidirectional port pull-up (8051 traditional I/O port)

Four modes can be set: quasi-bidirectional pull-up, strong push-pull pull-up, input only/high impedance and open drain

Each I/O port can drive up to 20mA, but the entire chip should not exceed 120mA.

â—If the I/O port is not enough, you can use the 3 common I/O lines to connect the 74HC595 (Â¥0.21) to expand the I/O port, and expand the dozens of I/O ports by multi-chip cascading. /D for key scan to save I / O port

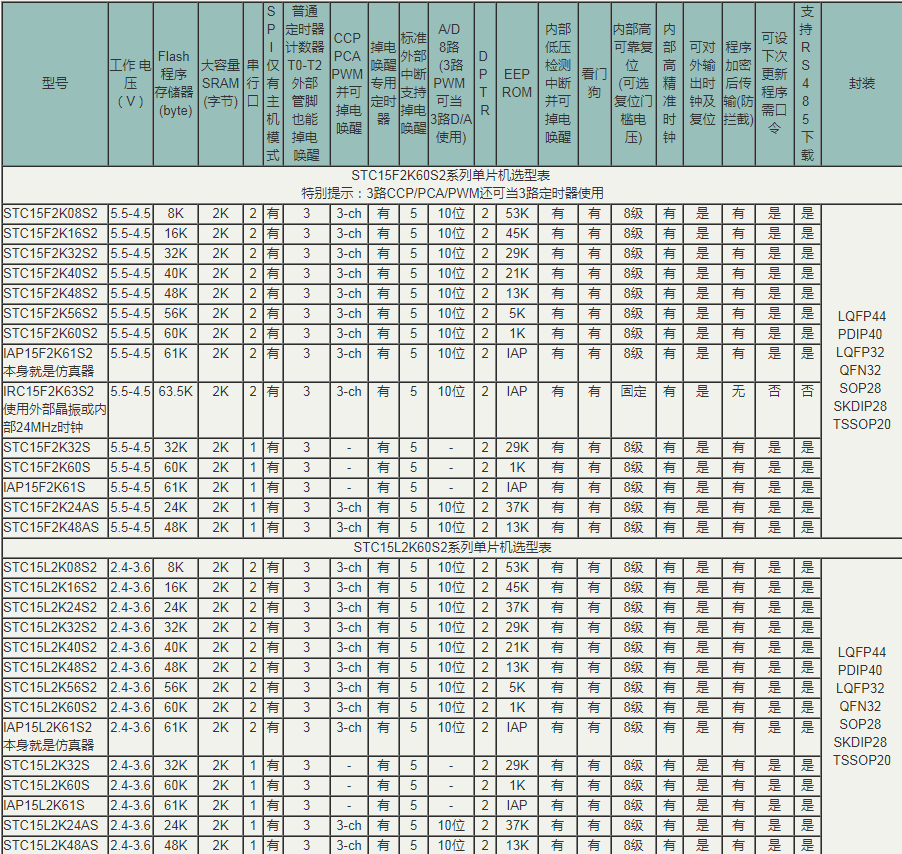

Reasons for choosing STC15F2K60S2 series MCU:

★ On-chip large capacity 2048 bytes SRAM

★Super encryption, Hongjing eighth generation encryption technology

★Super anti-interference:

1. High anti-static protection (ESD) machine easily over 20,000 volts static test

2. Easy 4KV fast pulse interference (EFT test)

3. Wide voltage, not afraid of power jitter

4. Wide temperature range, -40 ° C ~ +85 ° C

★ Dramatically reduce EMI (electromagnetic radiation), internal configurable clock, 1 clock / machine cycle, available low frequency clock

----Powerful guarantee to export to Europe and America

Ultra low power consumption:

1. Power-down mode: external interrupt wake-up power "0.1uA

2. Idle mode: typical power consumption "1mA,

3. Normal working mode: 4mA~6mA,

4. Power-down mode can be awakened by external interrupt or internal power-down wake-up timer, suitable for battery-powered systems, such as water meters, gas meters, portable devices, etc.

★In the system programmable (ISP), no programmer, no emulator, remote upgrade can send STC-ISP download programmer, 10,000 pieces / person / day

★ Can completely eliminate the external expensive reset circuit, internal integrated high-reliability reset circuit, ISP programming, 8-level reset threshold voltage optional, of course, can continue to use external reset circuit

★ It can completely eliminate the external expensive crystal clock, integrate high-precision R/C clock, ±1% temperature drift (-40°C~+85°C), and float at room temperature for 5‰.

Application of STC15F2K60S2 chip PWM1. purpose

Pulse Width Modulation (PWM) is a technique that uses a program to control the waveform duty cycle, period, and phase waveform. It is widely used in three-phase motor drive, D/A conversion, and other applications.

The PCA module of STC15 series MCU can work in 8-bit PWM or 7 by setting bits EBSn_1/PCA_PWMn.7 and EBSn_0/PCA_PWMn.6 in their respective registers PCA_PWMn (n=0,1,2. the same below). Bit PWM or 6-bit PWM mode.

2. And CCP / PWM / PCA applications related to the special function register symbol CCON CMOD CCAPM0 CCAPM1 CCAPM2 CL CH CCAP0L described PCA Control Register PCA Mode Register PCA Module 0 Mode Register PCA Module 1 Mode Register PCA Module 2 Mode Register PCA Base TImer Low PCA Base TImer High PCA Module-0 Capture Register Low PCA Module-0 Capture Register High PCA Module-1 Capture Register Low PCA Module-1 Capture Register High PCA Module-2 Capture Register Low PCA Module-2Capture Register High PCA PWM Mode Auxiliary Register 0 PCA PWM Mode Auxiliary Register 1 PCA PWM Mode Auxiliary Register 2-bit address and symbolic address D8H B7 CF B6 CR - B5 - - B4 - - CAPN0 CAPN1 CAPN2 B3 - B2 CCF2 B1 CCF1 B0 CCF0 reset value 00xx xx00 0xxx 0000 x000 000 x000 0000 x000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 00xx xx00 00xx xx00 00xx xx00 0100 0000 D9H CIDL DAH DBH DCH E9H F9H EAH - - - CPS2 CPS1 CPS0 ECF MAYPWMECCFTOG0 0 0 0 MAYPWMECCFTOG1 1 1 1 MAYPWMECCFTOG2 2 2 2 ECOCAPPM0 0 ECOCAPPM1 1 ECOCAPPM2 2 CCAP0H FAH CCAP1L EBH CCAP1H FBH CCAP2L ECH CCAP2H PCA_PWM0 PCA_PWM1 PCA_PWM2 AUXRI P_SW1 FCH F2H EBS0EBS0_1 _0 EBS1EBS1_1 _0 EBS2EBS2_1 _0 - - - - EPC0EPC0H L EPC1EPC1H L EPC2EPC2H L - DPS F3H - - - - F4H - - - SP1_S1 - SP1_S0 Auxiliary Register CCP_CCP_A2H S1_S1 S1_S0 1 S1 S0 2.1. PCA Operating Mode Register CMOD The format of the PCA Operating Mode Register is as follows: CMOD: PCA Operating Mode Register SFR name CCON Address D9H bit name B7 CIDL B6 - B5 - B4 - B3 CPS2 B2 CPS1 B1 CPS0 B0 ECF CIDL: Whether to stop the control bit of PCA counting in idle mode. When CIDL = 0, the PCA counter continues to operate in idle mode; when CIDL = 1, the PCA counter stops operating in idle mode; CPS2, CPS1, CPS0: PCA count pulse source select control bits. The PCA count pulse selection is shown in the table below. CPS2 CPS1 CPS0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 Select PCA/PWM clock source input 0, system clock, SYSclk/12 1, system clock, SYSclk/2 2. Timer 0 overflow pulse. Since Timer 0 can work in T1 mode, it can overflow by counting one clock, thus reaching the highest frequency CPU working clock SYSclk. By changing the overflow rate of Timer 0, the PWM output of adjustable frequency can be realized. 3, ECI/P1 .2 (or P4.1) external input clock (maximum rate = SYSclk/2) 4, system clock, SYSclk 5, system clock / 4, SYSclk / 4 6, system clock / 6, sysclk / 6, 7, system Clock/8, SYSclk/8 For example, when CPS2/CPS1/CPS0 = 1/0/0, the clock source of CCP/PCA/PWM is SYSclk, without timer 0.

The frequency of PWM is SYSclk/256.

If you want to use the system clock /3 as the clock source of PCA, you should select T0 overflow as the clock source of CCP/PCA/PWM. In this case, let T0 work in 1T mode, and count 3 pulses to generate overflow. With the overflow of T0, the system clock can be divided by 1~65536 (T0 works in 16 for reload mode).

ECF: PCA count overflow interrupt enable bit.

When ECF = 0, the CF bit interrupt in register CCON is disabled. When ECF = 1, the CF bit interrupt in register CCON is enabled.

2.2. PCA Control Register CCON

The format of the PCA Control Register is as follows: CCON: PCA Control Register SFR name CCON Address D8H bit name B7 CF B6 CR B5 - B4 - B3 - B2 - B1 CCF1 B0 CCF0 CF: PCA Counter Array Overflow Flag. When the PCA counter overflows, the CF is set by hardware. If the ECF bit of the CMOD register is set, the CF flag can be used to generate an interrupt. The CF bit can be set by hardware or software, but can only be cleared by software.

CR: PCA counter array run control bit. This bit is set by software and is used to start the counter array count. This bit is cleared by software and is used to turn off the PCA counter.

CCF2: PCA module 2 interrupt flag. This bit is set by hardware when a match or capture occurs. This bit must be cleared by software.

CCF1: PCA module 1 interrupt flag. This bit is set by hardware when a match or capture occurs. This bit must be cleared by software.

CCF0: PCA module 0 interrupt flag. This bit is set by hardware when a match or capture occurs. This bit must be cleared by software.

2.3. PCA compare/capture registers CCAPM0, CCAPM1 and CCAPM2

The format of the compare/capture register of PCA module 0 is as follows: CCAPM0: compare/capture register of PCA module 0 SFR name Address CCAPM0 DAH Bit name B7 - B6 ECOM0 B5 CAPP0 B4 CAPN0 B3 MAT0 B2 TOG0 B1 PWM0 B0 ECCF0 B7: Reserved for the future Use. ECOM0: Allows the comparator function control bit.

The comparator function is enabled when ECOM0 = 1. CAPP0: Positive capture control bit.

When CAPP0 = 1, a rising edge capture is allowed. CAPN0: Negative capture control bit.

When CAPN0 = 1, the falling edge capture is allowed. MAT0: Match control bit.

When MAT0 = 1, a match between the PCA count value and the module's compare/capture register value sets the interrupt flag bit CCF0 of the CCON register.

TOG0: Flip control bit.

When TOG0 = 1, it operates in the PCA high-speed pulse output mode, and the match of the value of the PCA counter with the value of the module's compare/capture register will cause the CCP0 pin to flip. PWM0: Pulse width modulation mode.

When PWM0 = 1, the CCP0 pin is allowed to be used as a pulse width adjustment output.

ECCF0: Enable CCF0 interrupt. The compare/capture flag CCF0 of the enable register CCON is used to generate an interrupt.

The format of the compare/capture register of PCA module 1 is as follows: CCAPM1: compare/capture register of PCA module 1 SFR name Address bit CCAPM1 DBH B7 B6 B5 B4 B3 B2 B1 B0 name - ECOM1 CAPP1 CAPN1 MAT1 TOG1 PWM1 ECCF1 B7: Reserved for the future Use. ECOM1: Allows the comparator function control bit.

The comparator function is enabled when ECOM1 = 1. CAPP1: Positive capture control bit.

When CAPP1 = 1, a rising edge capture is allowed. CAPN1: Negative capture control bit.

When CAPN1 = 1, the falling edge capture is allowed. MAT1: Match control bit.

When MAT1 = 1, a match between the PCA count value and the module's compare/capture register value sets the interrupt flag bit CCF1 of the CCON register. TOG1: Flip control bit.

When TOG1 = 1, it operates in PCA high-speed pulse output mode, and the match of the value of the PCA counter with the value of the module's compare/capture register will cause the CCP1 pin to flip. PWM1: Pulse width modulation mode.

When PWM1 = 1, the CCP1 pin is allowed to be used as a pulse width adjustment output.

ECCF1: Enable CCF1 interrupt. The compare/capture flag CCF1 of the enable register CCON is used to generate an interrupt. The format of the compare/capture register of PCA module 2 is as follows: CCAPM2: Comparison/capture register of PCA module 2 SFR name Address CCAPM2 DCH Bit name B7 - B6 B5 B4 B3 B2 B1 B0 ECOM2 CAPP2 CAPN2 MAT2 TOG2 PWM2 ECCF2 B7: Reserved for the future Use. ECOM2: Allows the comparator function control bits.

The comparator function is enabled when ECOM2 = 1. CAPP2: Positive capture control bit.

When CAPP2 = 1, the rising edge is allowed to capture. CAPN2: Negative capture control bit.

When CAPN2 = 1, the falling edge capture is allowed. MAT2: Match control bit.

When MAT2 = 1, a match between the PCA count value and the module's compare/capture register value sets the interrupt flag bit CCF2 of the CCON register. TOG2: Flip control bit.

When TOG2 = 1, it operates in PCA high-speed pulse output mode, and the match of the value of the PCA counter with the value of the module's compare/capture register will cause the CCP2 pin to flip. PWM2: Pulse width modulation mode.

When PWM2 = 1, the CCP2 pin is allowed to be used as a pulse width adjustment output.

ECCF2: Enable CCF2 interrupt. The compare/capture flag CCF2 of the enable register CCON is used to generate an interrupt. 2.4. PCA 16-bit timer - low 8-bit CL and high 8-bit CH

The CL and CH addresses are E9H and F9H, respectively, and the reset value is 00H, which is used to store the load value of PCA. 2.5. PCA Capture/Compare Register - CCAPnL (Low Byte) and CCAPnH (High Byte)

When the PCA modules are used for capture or comparison, they are used to hold the 16-bit capture count values ​​for each module; when the PCA module is used in PWM mode, they are used to control the duty cycle of the output. Where n = 0, 1, 2, corresponding to module 0, mode 1 and module 2, respectively. The reset value is 00H. Their corresponding addresses are:

CCAP0L — EAH, CCAP0H — FAH: Capture/compare register for module 0. CCAP1L — EBH, CCAP1H — FBH: Capture/Compare Register for Module 1. CCAP2L — ECH, CCAP2H — FCH: Capture/Compare Register for Block 2. 2.6. PCA module PWM registers PCA_PWM0, PCA_PWM1 and PCA_PWM2

The format of the PWM register of PCA module 0 is as follows: PCA_PWM0: PWM register SFR name of PCA module 0 PCA_PWM0 Address F2H Bit name B7 EBS0_1 B6 EBS0_0 B5 B4 B3 B2 - - - - B1 EPC0H B0 EPC0L EBS0_1, EBS0_0: When PCA module 0 works Function selection bit in PWM mode. 0,0: PCA module 0 works in 8-bit PWM function; 0,1: PCA module 0 works in 7-bit PWM function; 1,0: PCA module 0 works in 6-bit PWM function;

1,1: Invalid, PCA module 0 works in 8-bit PWM mode. EPC0H: In PWM mode, it consists of 9 digits with CCAP0H. EPC0L: In PWM mode, it forms 9 digits with CCAP0L.

The format of the PWM register of PCA module 1 is as follows: PCA_PWM1: PWM register SFR name of PCA module 1 PCA_PWM1 Address F3H Bit B7 B6 EBS2_0 B5 B4 B3 B2 - - - - B1 EPC1H B0 EPC1L name EBS2_1 EBS1_1, EBS1_0: When PCA module 1 works Function selection bit in PWM mode. 0,0: PCA module 1 works in 8-bit PWM function; 0,1: PCA module 1 works in 7-bit PWM function; 1,0: PCA module 1 works in 6-bit PWM function;

1,1: Invalid, PCA module 1 works in 8-bit PWM mode. EPC1H: In PWM mode, it consists of 9 digits with CCAP1H. EPC1L: In PWM mode, it consists of 9 digits with CCAP1L.

The format of the PWM register of PCA module 2 is as follows: PCA_PWM2: PWM register SFR name of PCA module 2 PCA_PWM2 Address F4H Bit name B7 EBS2_1 B6 EBS2_0 B5 - B4 - B3 - B2 - B1 EPC2H B0 EPC2L EBS2_1, EBS2_0: When PCA module 2 works Function selection bit in PWM mode. 0,0: PCA module 2 works in 8-bit PWM function; 0,1: PCA module 2 works in 7-bit PWM function; 1,0: PCA module 2 works in 6-bit PWM function;

1,1: Invalid, PCA module 2 works in 8-bit PWM mode. EPC2H: In PWM mode, it consists of 9 digits with CCAP2H. EPC2L: In PWM mode, it consists of 9 digits with CCAP2L.

PCA module working mode setting table are listed below: ECOMn 0 1 1 1 1 X CAPPn 0 0 1 0 1 1 CAPNn 0 0 0 1 1 0 MATn 0 0 0 0 0 0 TOGn PWMn ECCFn 0 0 0 0 0 0 0 1 1 1 1 0 0 0 1 1 1 X module function has no 8-bit PWM operation, no interrupt 8-bit PWM output, interrupt 8-bit PWM output is generated from low to high, and 8-bit PWM output is generated from high to low. High-to-low or low-to-high 16-bit capture mode, triggered by the rising edge of CEXn/PCAn XX 1 1 0 1 0 0 1 1 0 0 0 0 1 1 0 0 0 1 0 0 0 0 XXXX 16-bit capture mode The 16-bit capture mode is triggered by the falling edge of CEXn/PCAn. The 16-bit software timer 16-bit high-speed output PCA module operating mode setting is triggered by the CEXn/PCAn transition (CCAPMn register, n = 0, 1, 2) 3 . Schematic

3.1 8-bit pulse width adjustment mode (PWM)

When [EBSn_1, EBSn_0] = [0, 0] or [1, 1], the PCA module n operates in 8-bit PWM mode, at this time {0, CL[7:0]} and the capture register [EPCnL, CCAPnL[ 7:0]] for comparison.

The structure of the PWM mode is shown in the figure below.

EPCnHCCAPnHEPCnLCCAPnL[7:0] outputs 0enable9-bit comparator (0,CL[7:0])"(EPCnL,CCPnL[7:0])(0,CL[7:0])"=(EPCnL,CCPnL[7 :0]) Output 10CL[7:0]PWMnCL overflow_ECOMn1CAPPn0CAPNn0MATn0TOGn0PWMn1ECCFn0CCAPMn, n=0,1,2 Address: Dah, DBh, DCh

PCA PWM mode/modulatable pulse width output mode structure diagram (PCA module operates in 8-bit PWM mode) When the PCA module operates in 8-bit PWM mode, since all modules share the only PCA timer, all their output frequencies are the same. . The output duty cycle of each module is independently varied and is related to the capture registers {EPCnL, CCAPnL[7:0]} used. When the value of {0,CL[7:0]} is less than {EPCnL, CCAPnL[7:0]}, the output is low; when the value of {0,CL[7:0]} is equal to or greater than {EPCnL, CCAPnL When [7:0]}, the output is high. When the value of CL changes from FF to 00, the contents of {EPCnH, CCAPnH[7:0]} are loaded into {EPCnL, CCAPnL[7:0]}. This allows the PWM to be updated without interference. To enable PWM mode, the PWMn and ECOMn bits of the CCAPMn register of the module must be set.

PCA clock input source frequencyWhen the PWM is 8 bits: PWM frequency =

256

The PCA clock input source can be selected from the following 8: SYSclk, SYSclk/2, SYSclk/4, SYSclk/6,

SYSclk/8, SYSclk/12, Timer 0 overflow, ECI/P1.2 input.

If you want to achieve adjustable frequency PWM output, you can choose the overflow rate of timer 0 or the input of ECI pin as the clock input source of PCA/PWM.

When EPCnL = 0 and CCAPnL = 00H, the PWM fixed output is high. When EPCnL = 1 and CCAPnL = 0FFH, the PWM fixed output is low. When an I/O is used as PWM, the state of the port: The state of the previous port of the PWM is weak. Pull-up/quasi-bi-directional strong push-pull output/strong pull-up output is only input/high-resistance open-drain PWM output state strong push-pull output/strong pull-up output, to add output current limiting resistor 1K~10K strong push-pull output / Strong pull-up output, to add output current limiting resistor 1K~10K PWM invalid open drain 3.2 7-bit pulse width adjustment mode (PWM)

When [EBSn_1, EBSn_0] = [0, 1], the PCA module n operates in 7-bit PWM mode, at which time {0, CL[6:0]} and the capture registers [EPCnL, CCAPnL[6:0]] Comparison. The structure of the PWM mode is shown in the figure below.

EPCnHCCAPnHEPCnLCCAPnL[6:0] outputs 0enable8-bit comparator (0,CL[6:0])"(EPCnL,CCPnL[6:0])(0,CL[6:0])"=(EPCnL,CCPnL[6 :0]) Output 10CL[6:0]PWMnCL overflow_ECOMn1CAPPn0CAPNn0MATn0TOGn0PWMn1ECCFn0CCAPMn, n=0,1,2 Address: Dah, DBh, DCh

PCA PWM mode/modulatable pulse width output mode structure diagram (PCA module operates in 7-bit PWM mode) When the PCA module operates in 7-bit PWM mode, since all modules share the only PCA timer, all their output frequencies are the same. . The output duty cycle of each module is independently varied and is related to the capture registers {EPCnL, CCAPnL[6:0]} used. When the value of {0,CL[6:0]} is less than {EPCnL, CCAPnL[6:0]}, the output is low; when the value of {0,CL[6:0]} is equal to or greater than {EPCnL, CCAPnL When [6:0]}, the output is high. When the value of CL changes from 7F to 00, the contents of {EPCnH, CCAPnH[6:0]} are loaded into {EPCnL, CCAPnL[6:0]}. This allows the PWM to be updated without interference. To enable PWM mode, the PWMn and ECOMn bits of the CCAPMn register of the module must be set.

PCA clock input source frequencyWhen the PWM is 7 bits: PWM frequency =

128

The PCA clock input source can be selected from the following 8: SYSclk, SYSclk/2, SYSclk/4, SYSclk/6, SYSclk/8, SYSclk/12, Timer 0 overflow, ECI/P1.2 input.

If you want to achieve adjustable frequency PWM output, you can choose the overflow rate of timer 0 or the input of ECI pin as the clock input source of PCA/PWM.

When EPCnL = 0 and CCAPnL = 80H, the PWM fixed output is high. When EPCnL = 1 and CCAPnL = 0FFH, the PWM fixed output is low. 3.2 6-bit pulse width adjustment mode (PWM)

When [EBSn_1, EBSn_0] = [1, 0], the PCA module n operates in 6-bit PWM mode, at which time {0, CL[5:0]} and the capture registers [EPCnL, CCAPnL[5:0]] Comparison. The structure of the PWM mode is shown in the figure below.

EPCnHCCAPnHEPCnLCCAPnL[5:0] outputs 0enable7-bit comparator (0,CL[5:0])"(EPCnL,CCPnL[5:0])(0,CL[5:0])"=(EPCnL,CCPnL[5 :0]) Output 10CL[5:0]PWMnCL overflow_ECOMn1CAPPn0CAPNn0MATn0TOGn0PWMn1ECCFn0CCAPMn, n=0,1,2 Address: Dah, DBh, DCh

PCA PWM mode/modulatable pulse width output mode structure diagram (PCA module operates in 6-bit PWM mode) When the PCA module operates in 6-bit PWM mode, since all modules share the only PCA timer, all their output frequencies are the same. . The output duty cycle of each module is independently varied and is related to the capture registers {EPCnL, CCAPnL[5:0]} used. When the value of {0,CL[5:0]} is less than {EPCnL, CCAPnL[5:0]}, the output is

Low; when the value of {0,CL[5:0]} is equal to or greater than {EPCnL, CCAPnL[5:0]}, the output is high. When the value of CL changes from 3F to 00, the contents of {EPCnH, CCAPnH[5:0]} are loaded into {EPCnL, CCAPnL[5:0]}. This allows the PWM to be updated without interference. To enable PWM mode, the PWMn and ECOMn bits of the CCAPMn register of the module must be set.

PCA clock input source frequencyWhen the PWM is 6 bits: PWM frequency = 64

The PCA clock input source can be selected from the following 8: SYSclk, SYSclk/2, SYSclk/4, SYSclk/6, SYSclk/8, SYSclk/12, Timer 0 overflow, ECI/P1.2 input.

If you want to achieve adjustable frequency PWM output, you can choose the overflow rate of timer 0 or the input of ECI pin as the clock input source of PCA/PWM.

When EPCnL = 0 and CCAPnL = 0C0H, the PWM fixed output is high. When EPCnL = 1 and CCAPnL = 0FFH, the PWM fixed output is 4. program

//P3.7 output PWM waveform #include sfr CCON = 0xd8; sfr CMOD = 0xd9; sfr CCAPM2 = 0xdc; sfr CL = 0xe9; sfr CH = 0xf9;

Sfr CCAP2L = 0xec; sfr CCAP2H = 0xfc; sfr PCA_PMW2 = 0xf4;

Code unsigned char seven_seg[] = {0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90}; unsigned char cp1,cp2 = 255; unsigned int cp0;

Sbit P3_4 = P3^4; sbit P3_5 = P3^5; sbit P3_6 = P3^6;

Void TImer0_isr(void) interrupt 1 {

TH0 = (65536 - 1000) / 256; //Reload initial value TL0 = (65536 - 1000) % 256; //Reload initial value cp0++; //Interrupt 1 time, variable plus 1 if(cp0 》= 100) //1 second is up{

Cp0 = 0;

Cp2--; //cp2 is the pulse width control variable if(cp2 <<= 1) cp2 = 255; }

P2 = 0xff;

P3 = 0xff; switch(cp1) {

Case 0: P2 = seven_seg[cp2 % 100 % 10]; P3_6 = 0; break; case 1: P2 = seven_seg[cp2 % 100 / 10]; P3_5 = 0;; break; case 2: P2 = seven_seg[cp2 / 100]; P3_4 = 0; break; }

Cp1++;

If(cp1》= 3)cp1 = 0; }

/*********************Timer0 initialization function***********************/ void Timer0_init(void) {

TMOD = 0x01; //T0 working mode 1

TH0 = (65536 - 1000) / 256; / / machine pulse count 1000 full overflow caused interrupt TL0 = (65536 - 1000) % 256;

EA = 1; //Open total interrupt ET0 = 1; //Open T0 interrupt TR0 = 1; //Start timer T0 }

Void pwm0_init(void) {

CCON = 0x00; CL = 0x00; CH = 0x00;

PCA_PMW2 = 0x00; //8-bit PMW, the ninth bit of the duty cycle EPC0L is 0 CCAPM2 = 0x42; //Allow comparison, P3.7 output CCON = 0x40; //Allow PAC count}

Void main(void) {

Timer0_init(); pwm0_init(); while(1) {

If(CL == 0xff) {

CCAP2L = cp2; CCAP2H = cp2; } } }

The main pain points in obtaining customers in foreign trade are fierce market competition, high customer acquisition costs, low customer stickiness, and single marketing methods. With the changes in the market environment, traditional marketing methods have been unable to meet customer needs. Enterprises need innovative marketing methods and technical means to improve customer stickiness and loyalty, reduce customer acquisition costs, in order to obtain more business opportunities in the fierce market competition.

Car Seat

Guangdong ganzhou , https://www.cn-gangdao.com