In recent years, with the rapid growth of personal handheld multimedia devices, low-power design has become more and more important, and even become the key to determining the success of products, such as notebooks, PDAs, mobile phones and other fashion consumer and business electronics. The power supply time requirement for the battery is getting higher and higher, and the high power consumption becomes a constraining factor for prolonging the battery life.

The power consumption of CMOS digital circuits is mainly composed of three parts: hopping power consumption, short circuit power consumption and static leakage power consumption. Among them, the ratio of system power consumption is greater than 90%, which is called dynamic power consumption. For SoC, all design methods are built around dynamic power consumption. How to minimize dynamic power consumption from all levels and aspects will be the key content in speech decoding design.

1 Low-power design strategy for speech decoders SoC low-power design should be optimized from the top to the bottom of the design, mainly using low-power strategies at all levels, usually at the system level, algorithm level, structure level, Comprehensive consideration at the level of circuit level, place and route, and manufacturing process. Studies have shown that in addition to the manufacturing process, the design factors of high level of abstraction (system level, algorithm level, structure level) have a much greater impact on power consumption than other levels. Therefore, research on low-power design techniques at the system level, algorithm level, and structure level is very important.

1.1 System-Level Low-Power Design Strategies Reducing system-level power consumption actually reduces dynamic power consumption. The main method is that the clock adopts the power-down management mode to make the SoC operate in a sleep state when the SoC is in an idle state (only some devices are in operation); when the preset time comes, an interrupt is generated, and the interrupt wakes up. Device; or use the gate clock technology to stop the clock of the inactive module, thereby reducing system power consumption.

In addition, the multi-clock design is also an effective way to reduce the power consumption of the system, that is, a module with a small amount of computation uses a low-frequency clock; and a module with a large amount of computation uses a high-frequency clock.

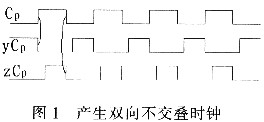

This design incorporates the above design strategies to reduce system power consumption. Use a system main frequency, through the fine control of the clock, that is, clock enable & disable to control the working state of the module; use the two-way non-overlapping clock technology to increase the operating frequency of the module with large computational complexity, while eliminating competition and risk Possible. The bidirectional non-overlapping clock is divided into two non-overlapping clocks by the system clock Cp, yCp and zCp. When the operation is as shown in Fig. 1, the input data is controlled by the yCp clock, and the result is controlled by the zCD clock.

This article refers to the address: http://

1.2 Algorithm-Level Low-Power Design Strategy Algorithm-level low-power design is mainly based on software code optimization, reducing unnecessary power consumption caused by low efficiency of the algorithm. On the one hand is the optimization of standard C code. C language is easy to read and portable, but in the actual engineering application, C language is not convenient for direct control of system hardware resources, and can not play the characteristics of SoC. Programming in assembly language can optimize and streamline the assembler according to the hardware structure of the chip itself, which can often make some complex algorithms and function modules achieve very good results in real-time processing. On the other hand, after analyzing the data correlation, control correlation and resource conflicts that affect the execution efficiency, the potential of the algorithm is fully exploited on the basis of manual assembly, and the hardware performance is maximized to achieve real-time requirements and low-power design indicators. .

In this design, based on the resources and instruction set features of the SoC platform, the software and hardware collaborative design method is used to convert the C code into assembly code. By analyzing the standard C algorithm, most of the loop and function calls are redundant, frequent. The function call operation (pull stack) takes up part of the processing time of the CPU. In the assembly code, it can be expanded by loop to reduce unnecessary loop judgment. The basic code of the basic principle is: ordinary single loop, one-time multiply accumulate (MAC) instruction in one cycle, and four loops in optimization after optimization. In the optimized code, four MACs are used at the same time, and when multiply and accumulate, the data of the next operation is extracted, the pipeline waiting is eliminated, the hardware resources are fully applied, and the efficiency is improved. In addition to loop unrolling, loop merges can also improve efficiency in some cases. The main reason is that each loop body needs to have a control command, and reducing the number of loops naturally reduces the number of control commands. Note that the two merged loops must have the same number of loops.

For functions that are used multiple times in the code, you should consider using the call instruction, which can greatly reduce the size of the code. For functions that only call a few times, you should embed the main function, because it can not only reduce the parameter transfer process. The instruction, and can reduce the push-pull operation of the calling function. Of course, for some large and complex functions, although it is only called once, but because the number of registers is limited, if you consider directly embedding the main function, you may have to do push and pop operations frequently, but you will not be able to pay for it. Call the instruction.

If some processing is more complicated, and the calculation amount is large and time-consuming in the whole decoding process, it is necessary to design the relevant hardware coprocessor, and directly operate the coprocessor through the assembly instruction, which can improve the efficiency, reduce the amount of calculation, and control the power consumption. But the cost will increase. This type of processing is especially critical and effective in modules that have significant real-time impact. For example, in the decoding of MP3, by increasing the matrix multiplier to improve the processing speed of the sub-band integrated filtering, a significant effect is obtained: the computation time can be reduced by 91%. This software and hardware collaborative design approach is used in many places in speech decoders.

In the algorithm level, other aspects of low-power design are also involved, such as reducing the number of memory accesses and shortening the width of the chip select signal. The design has also been processed accordingly. In general, algorithm-level optimization design has great potential in reducing system power consumption, which is of great significance for reducing the power consumption of the entire speech decoder.

1.3 Structure-Level Low-Power Design Strategies At the architecture level, the most important strategy for reducing power consumption is to utilize parallel processing or pipeline technology. After the pipeline is optimized, the read operation of the intermediate data can be reduced, and the read operation of the memory is reduced by about 50% compared with the serial processing, which is beneficial for reducing the power consumption of the system.

Since there are many modules for speech decoding, it can be found through research that each module can be pipelined by simply eliminating data correlation, which reduces the decoding time and thus reduces the clock frequency of real-time processing; in multi-channel speech processing, it can be used. Multi-channel parallel processing, adding processing modules to reduce processing time. In MP3 decoding, after stereo processing, subsequent processing of the left channel (alias reconstruction, IMDCT, sub-band synthesis filtering, etc.) and subsequent processing of the right channel can be performed in parallel, due to IMDCT (inverse modified discrete cosine transform) and subband synthesis Filtering is the most computationally intensive part of decoding, and the parallelism of the left and right channels can almost reduce the processing time of the system by half.

In order to increase the processing speed, it is also possible to exploit the internal parallel processing potential of the time-consuming module. For example, the IMDCT processing is a module that requires a large amount of computation in MP3 and ACC speech processing. Two multipliers can be placed inside the IMDCT, which allows two columns of data to be simultaneously processed and doubled in speed.

Obviously, increasing the processing speed by increasing the hardware mode does not reduce the amount of calculation, but the processing speed is increased, which is at the cost of increasing the chip area, resulting in an increase in cost, and must be comprehensively considered in processing to achieve a better cost performance.

The low-power design techniques at the circuit and process levels are primarily full-custom integrated circuit design techniques. Fully customized design can make full use of silicon wafers, layout, wiring, typesetting combination, etc. need to be adjusted repeatedly, design layout according to the optimal size, the most reasonable layout, the shortest connection, the most convenient pin, and the same function. Compared with the circuit implemented by the automatic place-and-route method, the manual design circuit can save more than half of the chip area, especially the use of latch-based manual place and route instead of automatic layout based on D flip-flops, reducing the area and system power consumption. Reduced by about 88%.

2 Conclusion Firstly, the physical composition of the power consumption of CMOS integrated circuits is analyzed, and the main power consumption is obtained. Secondly, different levels of SoC low-power design use different design methods, which focuses on the analysis of various strategies in the speech decoding to reduce system power consumption, and achieved initial results. The system level uses the bidirectional non-overlapping clock technology, which can reduce the operating frequency by 50%. The algorithm level mainly uses assembly language to rewrite and optimize the original code. After converting the C code decoded by MP3 into assembly code, the original 86 Kb is reduced. For 13 Kb, the A code decoded by AMR is converted to assembly code, which is reduced from the original 158Kb to 25 Kb. At the structure level, the coprocessor is added for parallel calculation, and 2 multipliers are placed inside the IMDCT, so that two can be calculated simultaneously. Column data, the speed is increased by 1 time. In the decoding of MP3, by increasing the matrix multiplier to improve the processing speed of sub-band synthesis filtering, the calculation time can be reduced by 91%.

1.ANTENK Wire to Board connectors are avialable in different terminations and sizes intended for use on a variety of applications. These connectors provide power and signal with different body styles, termination options, and centerlines. To find the wire to board set required, click on the appropriate sub section below.

2.Our products are widely used in electronic equipments,such as monitors ,electronic instruments,computer motherboards,program-controlled switchboards,LED,digital cameras,MP4 players,a variety of removable storage disks,cordless telephones,walkie-talkies,mobile phones,digital home appliances and electronic toys,high-speed train,aviation,communication station,Military and so on

Antenk Wire To Board Connectors Ranges:

Power Wire to Board

IDC Wire to Board

Locking Wire to Board

Latching Wire to Board

Fine Pitch Wire to Board

Wire to Board Connectors Information

Description

Wire-to-board connectors are used to interconnect printed circuit boards (PCBs) by using connectors attached to wires.

Specifications

Specifications for a wire to board connector include the following.

Wire-entry angle - There are three wire-entry angle styles: vertical, right-angle, and bottom-entry.

Wire size - Wire size is usually measured in American wire gauge (AWG), a standard for non-ferrous wire conductor sizes. The term "gauge" refers to the wire`s diameter. The higher the gauge number, the smaller the diameter and the thinner the wire.

Circuits or positions - With wire to board connectors, the number of circuits or positions may range from 1 to 120.

Pitch or center spacing - Pitch or center spacing is measured in millimeters (mm) or inches.

Lock to mating style - There are three basic lock-to-mating styles: positive, friction, and friction ramp.

Maximum current - The maximum current or current-carrying capacity is measured in amperes (A) and ranges from 1.0 A to 50. A.

Termination Methods

Crimp is the physical compression of a contact wire around a conductor to make an electrical and mechanical connection. Insulation displacement connectors (IDC) slice through the cable insulation to make a connection. Choices for termination method also include cage clamp, screw, tabs, and solder cups.

PCB Mounting Styles

With wire to board connectors, there are four choices for PCB mounting.

Through-hole technology (THT) mounts components on a PCB by inserting component leads through holes in the board and then soldering the leads in place on the opposite side of the board.

Surface mount technology (SMT) adds components to a PCB by soldering component leads or terminals to the top surface of the board. SMT components have a flat surface that is soldered to a flat pad on the face of the PCB. Typically, the PCB pad is coated with a paste-like formulation of solder and flux.

Press-fit and compression-style Board To Board Connectors are also commonly available.Wire to Board Connectors Information

Standards

Wire-to-board connectors carry approvals from various national and international organizations. In North America, they often bear marks from Underwriters Laboratories (UL) and/or the Canadian Standards Association (CSA).

A wire to board connector for the European marketplace should comply with the Restriction of Hazardous Substances (RoHS) and Waste Electrical and Electronic Equipment (WEEE) directives from the European Union (EU). Wire-to-board connectors that comply with other requirements are also available.

BS 9526 N0001 - Specification for multi-contact edge socket electrical connectors.

Wire To Board Connectors,Wire Harness,Pcb Wire To Board Connector,Pin Wire To Board Connector,IDC Wire to Board,Locking Wire to Board,Latching Wire to Board,Fine Pitch Wire to Board

ShenZhen Antenk Electronics Co,Ltd , https://www.atkconnectors.com