In ECM, FPGA, RT, and host are involved. How do you transfer data streams between the three? This article will take cRIO-9068 as an example to let you know the whole programming and implementation process.

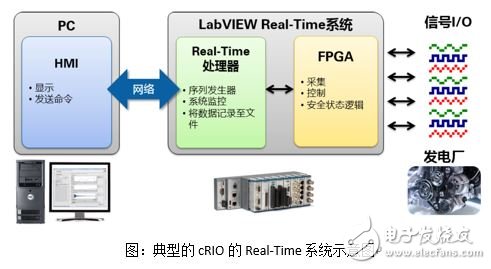

I. Overview of communication between FPGA, RT, and host data streamsIn a Real-TIme system with FPGA, the FPGA is responsible for collecting signals, then transmitting the collected data to the RT for monitoring and processing, and simultaneously displaying, recording or sending commands on the host. A typical cRIO-based Real-TIme system is shown below:

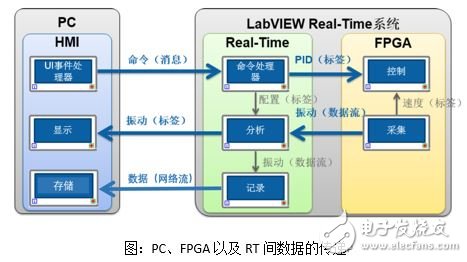

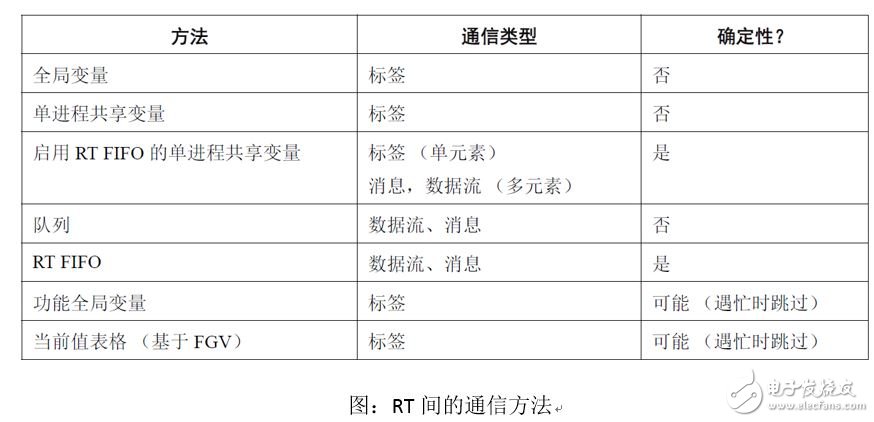

Data is mainly divided into two types in the Real-TIme system. One is such as messages, commands, etc. We only focus on the latest values ​​of such data, mainly through tags and messages, and the other is data streams. We need to get all the data information, not just the latest values, mainly through the network stream, FIFO.

For the data collected by the capture card, we sometimes want to record it and display it on the Host side. Usually, FPGA and RT use the FIFO for data stream transmission, while RT uses network stream and host to transmit data. This article will take cRIO-9068 as an example to show the whole process from signal acquisition to PC display, to help you better understand the data processing method of Real-TIme system.

Second, hardware & software Number card: NI 9263

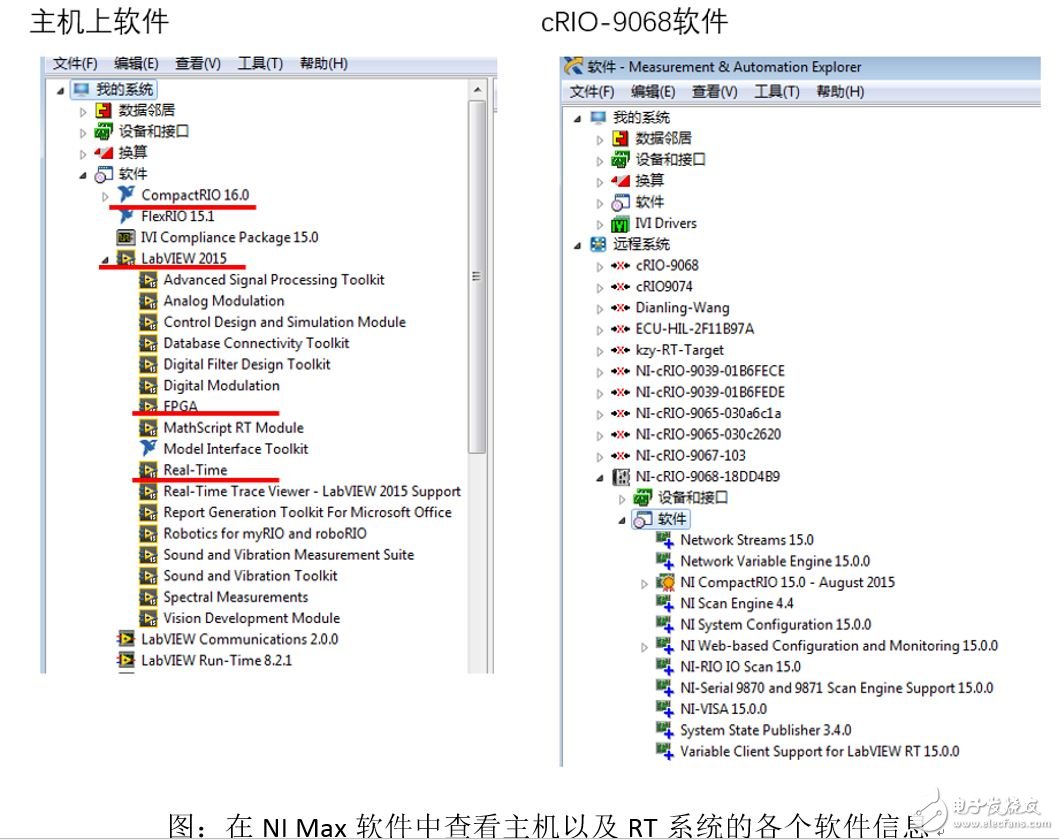

Equipment: cRIO-9068; RIGOL oscilloscope Software: LabVIEW; LabVIEW Real-Time; LabVIEW FPGA; CompactRIO

(You can view the software, drivers, and module versions installed in NI Max, and keep the software version in cRIO-9068 correct)

Finally, the hardware connection is as shown.

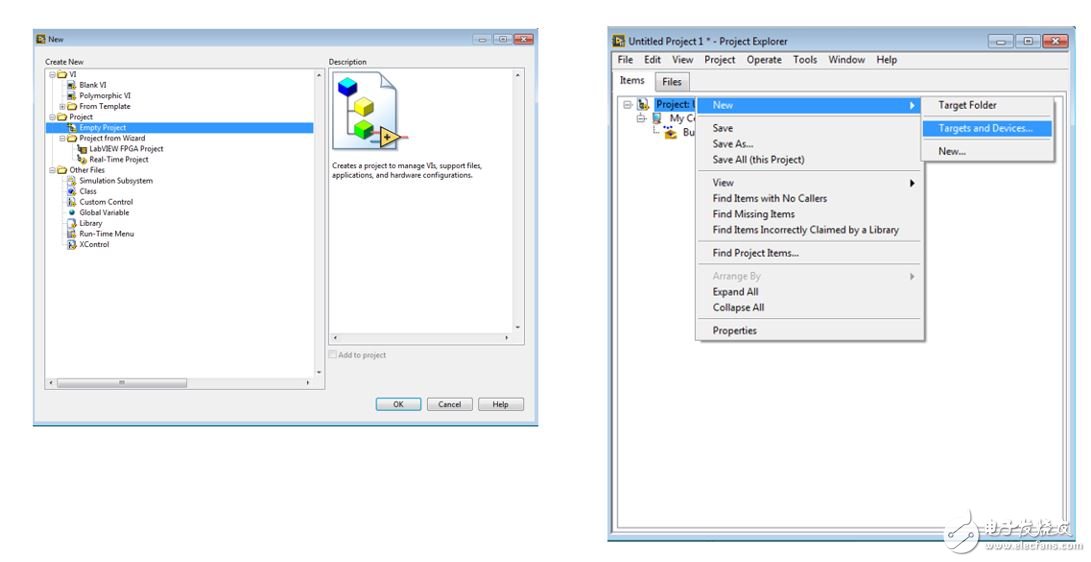

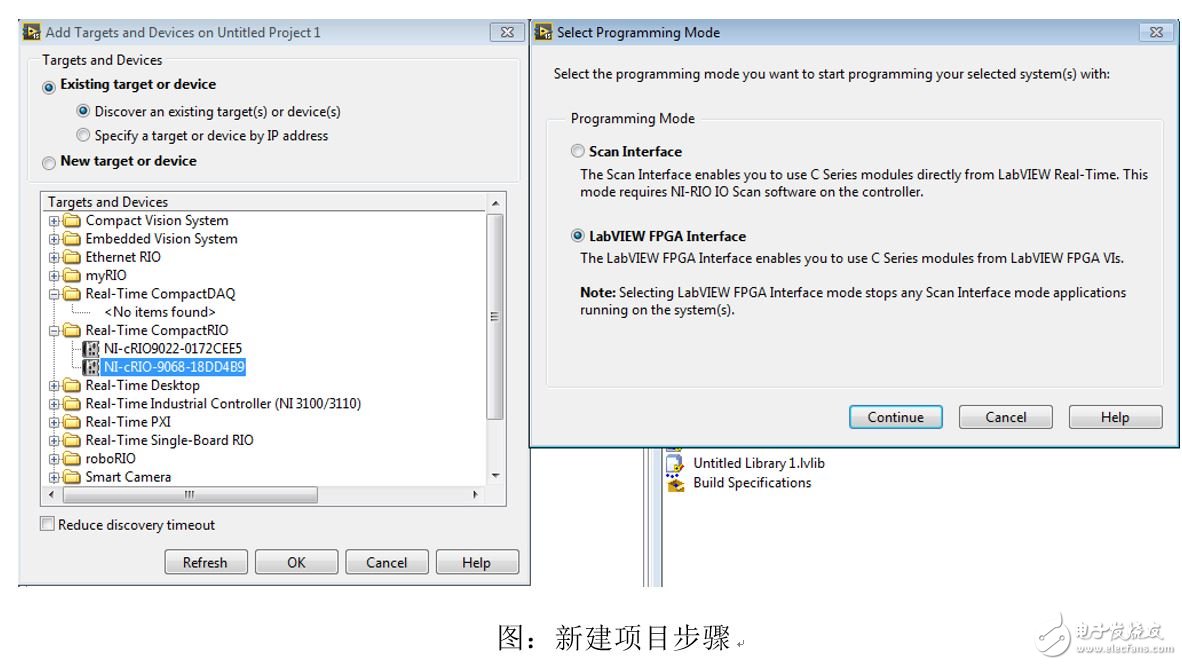

1) New Project Open LabVIEW, create a new project, right-click on my project in the project browser, select Add Target Device, and add hardware cRIO-9068 and NI 9263 to the newly created project.

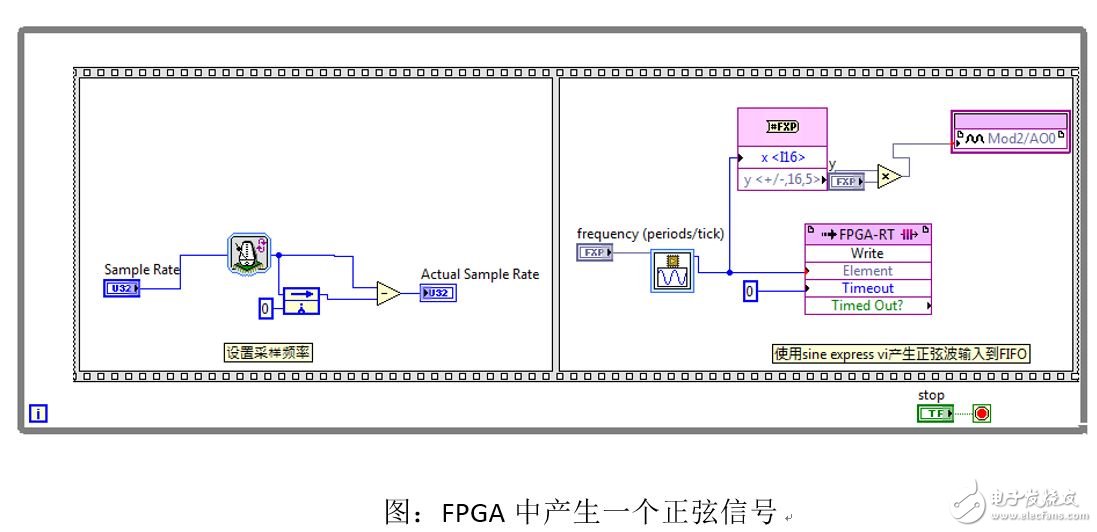

2) Design of FPGA.vi First we need to generate a sinusoidal signal in the FPGA, which is output via the analog port of the NI 9263.

Note: Single-cycle Timed Loops cannot be used here because the vi cannot be executed within one clock tick. About the single-cycle Timed Loop reference link:

Since the sine wave signal generated by the FPGA is transmitted to the RT terminal for display processing, etc., it belongs to the data stream transmission, so we use the DMA FIFO() here.

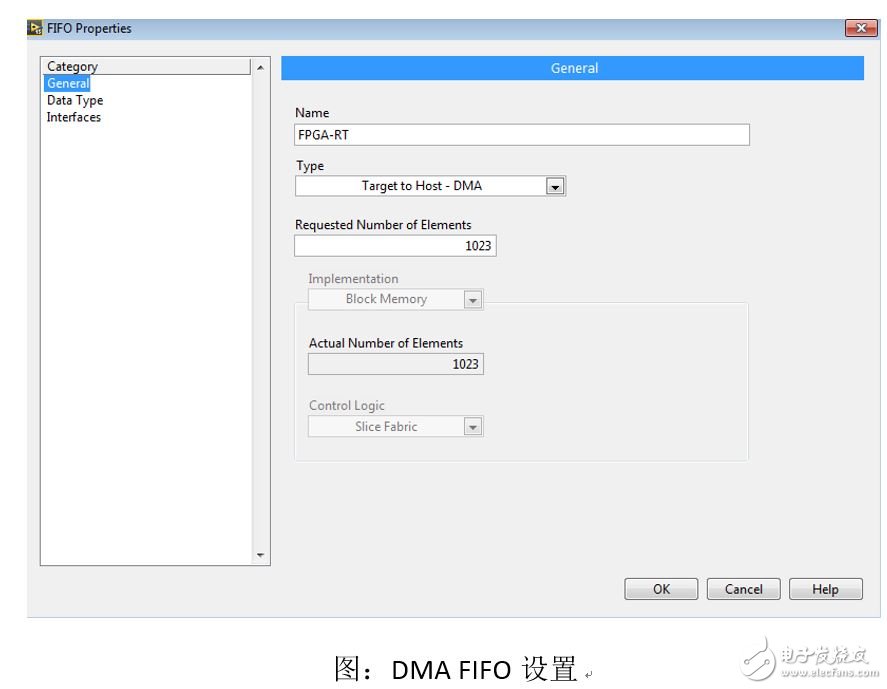

In the project browser, right click on the FPGA and create a new FIFO. The FIFO settings are as follows:

The type is selected at Type: Target to Host-DMA, and the size can be used by default. Select the type of data in the Data Type, here we are transmitting unsigned 32-bit data, so choose U32.

3) Design of RT.vi

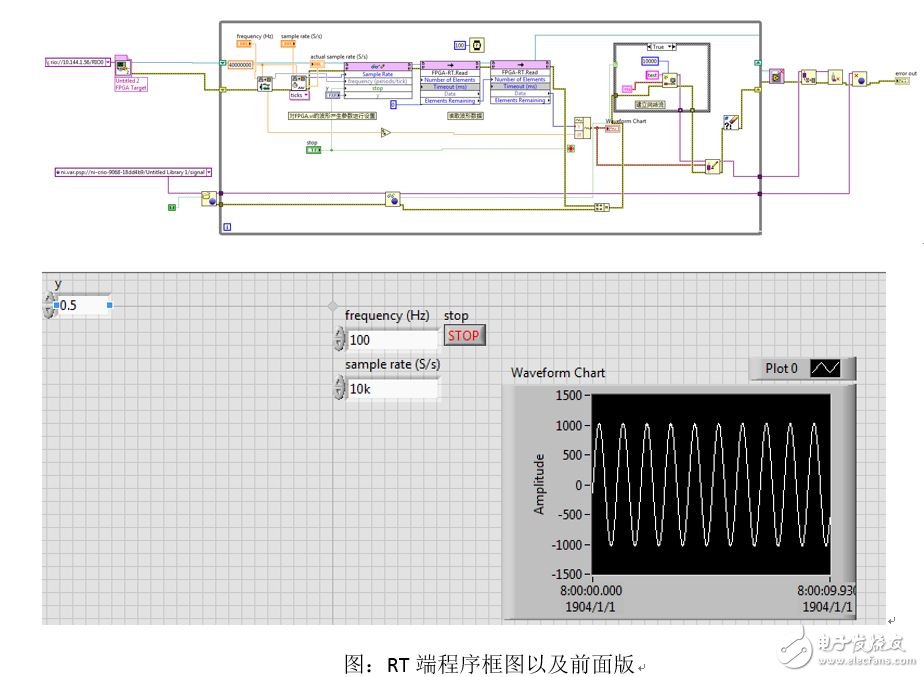

The RT end of the RT is mainly composed of two parts, one is to read the data transmitted from the FPGA from the FIFO, and the other is to establish a network flow and transmit the data to the host for detection. The important thing to note here is that since we need to open the host to read the data at any time, the host program runs.

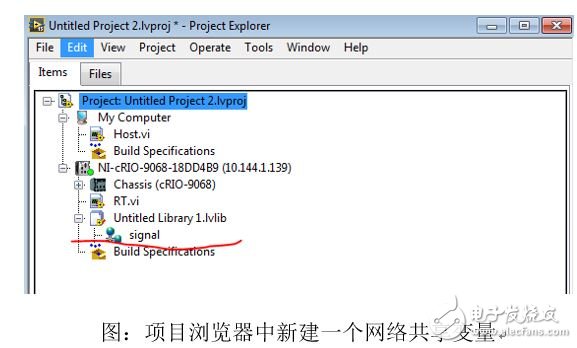

The RT end of the RT is mainly composed of two parts, one is to read the data transmitted from the FPGA from the FIFO, and the other is to establish a network flow and transmit the data to the host for detection. It should be noted here that since we need to open the host to read data at any time, when the host program runs, it will generate a signal to enable the network end of the RT side to establish and write data. Therefore, we create a new Boolean variable as the pass signal.

Therefore, on the RT side, we mainly use two methods for data transfer to the host, one is the network flow for each data transfer; the other is the network variable, which gets the latest value of the Boolean control.

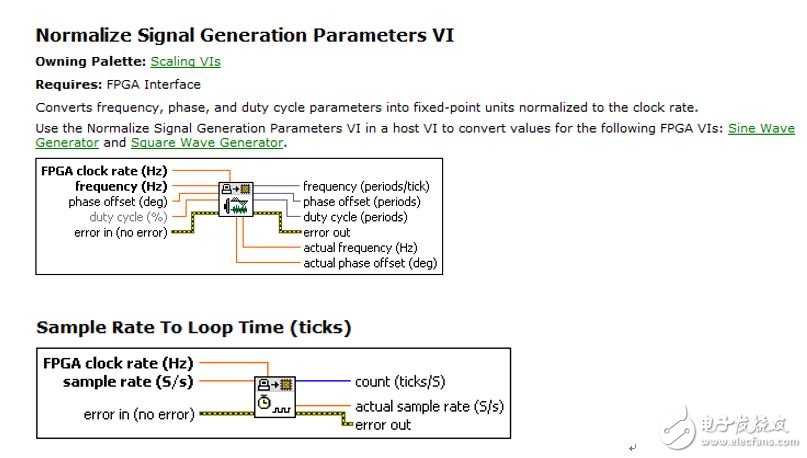

In the process of transferring FIFO waveforms, the following two numbers are often used. Here is a little more introduction.

Normalize Signal Generation Parameters & Sample Rate To Loop Time

Harvester Guide Rail,Harvester Conveyor Belts,Manure Spreader Accessories,Heavy Duty Clutch Plates

Changzhou Youeryou Trading Co., Ltd. , https://www.farmpartssupplier.com