This article is mainly about the introduction of norflash, and focuses on the characteristics of norflash in detail.

What are the 8 common features of norflash memoryNOR Flash

NOR FLASH is a very common memory chip, and the data will not be lost when power is off. NOR FLASH supports Execute On Chip, that is, the program can be executed directly in the FLASH chip (this means that the program stored on the NOR FLASH does not need to be copied to RAM You can run it directly). This is different from NAND FLASH. Therefore, in an embedded system, NOR FLASH is very suitable as a storage medium for the startup program. The reading of NOR FLASH is very similar to RAM (as long as the address of the data can be provided, the data bus can correctly give the data), but not Write directly. The write operation to NOR FLASH needs to follow a specific command sequence, and finally the control unit inside the chip completes the write operation.

NOR and NAND are the two main non-volatile flash memory technologies currently on the market. Intel first developed the NOR flash technology in 1988, which completely changed the original dominance of EPROM and EEPROM. Then, in 1989, Toshiba announced the NAND flash structure, emphasizing lower cost per bit, higher performance, and can be easily upgraded through an interface like a disk. But after more than ten years, there are still quite a few hardware engineers who can't distinguish between NOR and NAND flash memory.

Like "flash memory" can often be used interchangeably with the phase "NOR memory". Many people in the industry are also confused about the advantages of NAND flash memory technology over NOR technology, because in most cases flash memory is only used to store a small amount of code, NOR flash memory is more suitable at this time. And NAND is an ideal solution for high data storage density.

The characteristic of NOR is the execution on the chip (XIP, eXecute In Place), so that the application program can be run directly in the flash memory without reading the code into the system RAM. The transmission efficiency of NOR is very high, and it is very cost-effective in the small capacity of 1 to 4MB, but the very low writing and erasing speed greatly affects its performance.

NAND structure can provide extremely high cell density, can reach high storage density, and the speed of writing and erasing is also very fast. The difficulty of applying NAND is that the management of flash requires a special system interface.

Interface difference

NOR flash has an SRAM interface, there are enough address pins to address, you can easily access every byte inside.

NAND read and write operations use 512-byte blocks, which is a bit like a hard disk to manage such operations. Naturally, NAND-based memory can replace hard disks or other block devices.

Capacity cost

The cell size of NAND flash is almost half of that of NOR devices. Due to the simpler production process, the NAND structure can provide higher capacity within a given mold size, which reduces the price accordingly.

NOR flash occupies most of the flash memory market with a capacity of 1 to 16MB, while NAND flash is only used in products with a capacity of 8 to 128MB. This also shows that NOR is mainly used in code storage media, NAND is suitable for data storage, and NAND is used in CompactFlash, Secure Digital, PC Cards and MMC (Multi Media Card) have the largest market share in the memory card market.

Reliable and durable

One important consideration when using flash media is reliability. For systems that need to expand MTBF (Mean Time Between Failures), Flash is a very suitable storage solution. The reliability of NOR and NAND can be compared in terms of life (endurance), bit swapping, and bad block handling.

Life (durability)

In NAND flash memory, the maximum number of erasing and writing of each block is one million, while the number of erasing and writing of NOR is 100,000. In addition to NAND memory having the advantage of a block erase cycle of 10 to 1, the typical NAND block size is one-eighth of the NOR device, and each NAND memory block has fewer deletes in a given time.

Bit swap

All flash devices suffer from bit swapping. In some cases (rarely, NAND occurs more often than NOR), a bit will be inverted or reported to be inverted.

A bit change may not be obvious, but if it happens to a critical file, this small failure may cause the system to shut down. If you just report a problem, read it a few more times and it may solve it.

Of course, if this bit is really changed, an error detection/error correction (EDC/ECC) algorithm must be used. The problem of bit inversion is more common in NAND flash memory. When NAND flash memory is used, NAND suppliers recommend using EDC/ECC algorithms at the same time.

This problem is not fatal when using NAND to store multimedia information. Of course, if local storage devices are used to store operating systems, configuration files or other sensitive information, EDC/ECC systems must be used to ensure reliability.

Bad block handling

Bad blocks in NAND devices are randomly distributed. There have been previous efforts to eliminate bad blocks, but it was found that the yield rate was too low and the price was too high to be cost-effective.

NAND devices need to perform an initial scan of the medium to find bad blocks and mark the bad blocks as unusable. In the manufactured device, if this treatment cannot be carried out by a reliable method, it will lead to a high failure rate.

Easy to use

NOR-based flash memory can be used very directly, can be connected like other memories, and code can be run directly on it.

Because of the need for I/O interfaces, NAND is much more complicated. Access methods for various NAND devices vary from manufacturer to manufacturer.

When using a NAND device, you must write the driver first before you can continue to perform other operations. Writing information to NAND devices requires considerable skill, because designers must never write to bad blocks, which means that virtual mapping must be performed on NAND devices from beginning to end.

software support

When discussing software support, a distinction should be made between basic read/write/erase operations and higher-level software for disk emulation and flash management algorithms, including performance optimization.

Running code on NOR devices does not require any software support. When the same operation is performed on NAND devices, a driver is usually required, which is the memory technology driver (MTD). NAND and NOR devices are used for writing and erasing operations. Both require MTD (Memory Technology Devices).

When using NOR devices, the MTD required is relatively less. Many manufacturers provide more advanced software for NOR devices, including M-System's TrueFFS driver, which is used by Wind River System, Microsoft, QNX Software System, Symbian And Intel and other manufacturers.

The driver is also used to emulate DiskOnChip products and manage NAND flash memory, including error correction, bad block handling, and wear leveling.

NOR Flash erasing and its principleThe reading of NOR FLASH is very similar to RAM (as long as the address of the data can be provided, the data bus can give the data correctly), but it cannot be directly written. The write operation to NOR FLASH needs to follow a specific command sequence, and finally the control unit inside the chip completes the write operation.

From the point of view of the smallest supported access unit, NOR FLASH is generally divided into 8-bit and 16-bit (of course, there are also many NOR FLASH chips that support both 8-bit mode and 16-bit mode. The specific working mode is carried out through specific pins. select).

For 8-bit NOR FLASH chips, or chips working in 8-BIT mode, one address corresponds to one BYTE (8-BIT) data. For example, an 8-BIT NOR FLASH, assuming the capacity is 4 BYTE. The chip should have 8 data signals D7-D0 and 2 address signals, A1-A0. Address 0x0 corresponds to the 0th BYTE, and address 0x1 corresponds to 1 BYTE. , Address 0x2 corresponds to the second BYTE, and address 0x3 corresponds to the third BYTE. For a 16-bit NOR FLASH chip or a chip working in 16-BIT mode, an address corresponds to a HALF-WORD (16-BIT) data. For example, a 16-BIT NOR FLASH, assuming its capacity is 4 BYTE. The chip should have 16 data signal lines D15-D0 and 1 address signal A0. Address 0x0 corresponds to the 0th HALF-WORD inside the chip , Address 0x1 corresponds to the first HALF-WORD inside the chip

FLASH is generally divided into many SECTORs, and each SECTOR includes a certain number of storage units. For some large-capacity FLASH, it is also divided into different banks, each bank includes a certain number of SECTOR. The erasing operation of FLASH is generally based on SECTOR, BANK or the entire FLASH as the unit.

When writing to FLASH, each BIT can be programmed from 1 to 0, but 0 cannot be changed to 1. In order to ensure the correctness of the write operation, the erase operation must be performed before the write operation . The erase operation will change the value of a SECTOR of FLASH, a BANK or the entire FLASH to 0xFF. In this way, the write operation can be completed correctly.

Since NOR FLASH does not have local bad area management, once the storage block is damaged, the software or driver must take over the problem, otherwise it may cause the device to malfunction. When unlocking, erasing or writing the NOR FLASH block, the special command will first write the first page (Page) of the mapped memory area. Then the flash memory chip will provide a list of available instructions to the physical driver, and these instructions are defined by the CommON FLASH memory interface (CFI). Unlike ROM used for random access, NOR FLASH can also be used on storage devices; however, compared with NAND FLASH, the writing speed of NOR FLASH is generally much slower.

2. NOR Flash programming method

The following content, unless otherwise specified, the processor refers to the ARM processor, and FLASH refers to NOR FLASH. In addition, BYTE refers to the 8-BIT data unit, and HALF-WORD refers to the 16-BIT data unit , And WORD represents the 32-BIT data unit.

2.1 Processor addressing

ARM can be said to be the most popular 32-bit embedded processor. I only mention the addressing of the ARM processor here, as a solo exhibition for the future. From the perspective of the processor, each address in the system corresponds to a BYTE data unit. This is the same as many other processors.

2.2 Hardware connection between processor and NOR FLASH

From the previous introduction, we know that from the perspective of the processor, each address corresponds to a BYTE data unit. However, each address of NOR FLASH may correspond to a BYTE data unit, or it may correspond to a HALF-WORD data unit. So in the hardware design, when connecting the ARM processor and NOR FLASH, the address signal must be specially processed according to the actual situation.

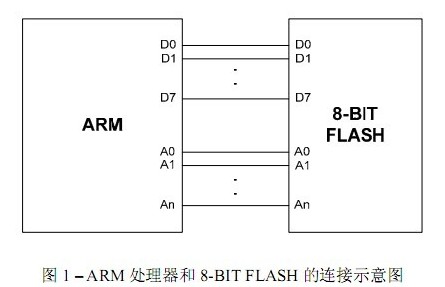

If the external expansion of the ARM processor is 8-BIT NOR FLASH, the connection of the data line and the address line should be as shown in Figure 1. From the figure, we can see that the data signals D0-D7 of the processor and the data signals D0-D7 of FLASH are connected one by one, and the address signal A0-An of the processor and the address signal A0-An of NOR FLASH are also corresponding one by one. connected.

If the external extension of the ARM processor is a 16-BIT NOR FLASH, the address line must be connected in a wrong position. Figure 2 shows a schematic diagram of the connection between an ARM processor and 16-BIT NOR FLASH. As shown in Figure 2, the data signals D0-D15 of the ARM processor and the data signals D0-D15 of the FLASH correspond one by one. The address signal of the ARM processor and the address signal of NOR FLASH are connected in a misplaced manner. ARM's A0 is suspended, ARM's A1 is connected to FLASH's A0, ARM's A2 is connected to FLASH's A1, and so on. The reason for the need for misaligned connection is: each address of the ARM processor corresponds to a BYTE data unit, and each address of the 16-BIT FLASH corresponds to a HALF-WORD (16-BIT) data unit. In order to maintain matching, it must be connected in a misaligned position. In this way, the lowest bit A0 of the address signal sent from the ARM processor is shielded from the 16-BIT FLASH.

NOR Flash programming method-the ignorant-casual writing by the ignorant

Supplementary note:

Generally speaking, the corresponding register must be set inside the ARM processor to tell the processor the bit width of the externally expanded FLASH (8-BIT/16-BIT/32-BIT). In this way, the processor knows how to correctly read data from FLASH when accessing;

Some ARM processors can set the address misalignment inside. For processors that support software selection of address misalignment, when connecting 16-BIT FLASH, the hardware does not need to misalign the address line. When designing, please refer to the MCU's data manual, which shall prevail, so as not to cause unnecessary trouble;

If the processor supports internally set address misalignment, during actual access, the sent address is actually misaligned inside the MCU, and its effect is equivalent to a misalignment on the hardware connection.

The above description may be more abstract, let us look at an example of 2 ARM processors accessing 16-BIT FLASH:

Example 1: ARM processor needs to read a BYTE from address 0x0

The ARM processor sends a signal 0x0 on the address line An-A0;

16-BIT FLASH sees the address 0x0 on its address signal An-A0, and then outputs the 16-BIT data unit corresponding to address 0x0 to D15-D0;

The ARM processor knows that it is accessing the 16-BIT FLASH, and reads the required BYTE data from D7-D0.

Example 2: ARM processor needs to read a BYTE from address 0x1

The ARM processor sends a signal 0x1 on the address line An-A0;

The address seen by 16-BIT FLASH on its address signal An-A0 is still 0x0, and then the 16-BIT data unit corresponding to address 0x0 is output to D15-D0;

The ARM processor knows that the 16-BIT FLASH is accessed, and it reads the required BYTE data from D15-D8.

2.3 Viewing the connection between ARM processor and NOR FLASH from a software perspective

To understand the connection between ARM processor and FLASH from a software perspective. For the connection of 8-BIT FLASH, it is well understood, because each address of the ARM processor and 8-BIT FLASH corresponds to a BYTE data unit. So there is no doubt that the address connection corresponds one by one. If the ARM processor is connected to a 16-BIT processor, because each address of the ARM processor corresponds to a BYTE data unit, and each address of the 16-BIT FLASH corresponds to a HALF-WORD 16- The data unit of BIT. Therefore, there is no doubt that when the ARM processor accesses the 16-BIT processor, the address must be staggered by one bit. When writing the FLASH driver, we don't need to know whether the address misalignment is realized by hardware or by setting the internal registers of the ARM processor. We only need to remember 2 points:

When the ARM processor accesses 8-BIT FLASH, the addresses correspond one by one;

When the ARM processor accesses the 16-BIT FLASH, the address must be misplaced.

2.4 8-BIT FLASH Programming Driver Example-HY29F040

HY29F040 is an 8-BIT NOR FLASH of Hyundai. In this section, we take this chip as an example to describe how to operate 8-BIT NOR FLASH.

The capacity of HY29F040 is 512K-BYTE, including 8 SECTORs in total, and the capacity of each SECTOR is 64K-BYTE. The chip supports SECTOR erase, block erase and write operations with BYTE as the basic unit. The command definition of HY29F040 is as follows Table-1 shows.

Next, let's take a look at how to implement basic erase and program operations. In the description later in this section, we use the following 2 definitions:

U32 sysbase; //This variable is used to indicate the starting address of FLASH

#define SysAddr8(sysbase, offset) ((volatile U8*)(sysbase)+(offset)) //Used to facilitate operations on the specified FALSH address

The macro SysAddr8 defines a BYTE (8-BIT) pointer whose address is (sysbase + offset). Assuming that the starting address of FLASH is 0x10000000, if you want to

Write 0xAB to the first BYTE of FLASH, you can use the following code:

*SysAddr8 (0x10000000, 0x1) = 0xAB;

note:

In the description later in this section, sysbase represents the start address of FLASH, and the offset in SysAddr8 represents the BYTE offset relative to the start address of FLASH. The offset is also 8-BIT FLASH in its own address signal An -The address seen on A0.

a. Whole chip erase operation

The entire chip erase operation requires a total of 6 cycles of bus write operations:

Write 0xAA to FLASH address 0x5555;

Write 0x55 to FLASH address 0x2AAA;

Write 0x80 to FLASH address 0x5555;

Write 0xAA to FLASH address 0x5555;

Write 0x55 to FLASH address 0x2AAA;

Write 0x10 to FLASH address 0x5555.

Corresponding code:

*SysAddr8 (sysbase, 0x5555) = 0xAA; //Write the value 0xAA to FLASH address 0x5555

*SysAddr8 (sysbase, 0x2AAA) = 0x55; //Write the value 0x55 to FLASH address 0x2AAA

*SysAddr8 (sysbase, 0x5555) = 0x80; //Write the value 0x80 to FLASH address 0x5555

*SysAddr8 (sysbase, 0x5555) = 0xAA; //Write the value 0xAA to FLASH address 0x5555

*SysAddr8 (sysbase, 0x2AAA) = 0x55; //Write the value 0x55 to FLASH address 0x2AAA

*SysAddr8 (sysbase, 0x5555) = 0x10; //Write the value 0x10 to the FLASH address 0x5555

b. SECTOR erase operation

The erase operation of SECTOR requires a total of 6 cycles of bus write operations:

Write 0xAA to FLASH address 0x5555;

Write 0x55 to FLASH address 0x2AAA;

Write 0x80 to FLASH address 0x5555;

Write 0xAA to FLASH address 0x5555;

Write 0x55 to FLASH address 0x2AAA;

Write 0x30 to the address corresponding to the SECTOR to be erased.

Corresponding code:

*SysAddr8 (sysbase, 0x5555) = 0xAA; //Write the value 0xAA to FLASH address 0x5555

*SysAddr8 (sysbase, 0x2AAA) = 0x55; //Write the value 0x55 to FLASH address 0x2AAA

*SysAddr8 (sysbase, 0x5555) = 0x80; //Write the value 0x80 to FLASH address 0x5555

*SysAddr8 (sysbase, 0x5555) = 0xAA; //Write the value 0xAA to FLASH address 0x5555

*SysAddr8 (sysbase, 0x2AAA) = 0x55; //Write the value 0x55 to FLASH address 0x2AAA

*SysAddr8 (sysbase, addr) = 0x30; //Write the value 0x30 to the address corresponding to the SECTOR to be erased

c. BYTE erase operation

Writing a BYTE data to FLASH requires 4 cycles of bus write operation:

Write 0xAA to FLASH address 0x5555;

Write 0x55 to FLASH address 0x2AAA;

Write 0xA0 to FLASH address 0x5555;

Write the programming data (BYTE) to the corresponding programming address.

Corresponding code:

*SysAddr8 (sysbase, 0x5555) = 0xAA; //Write the value 0xAA to FLASH address 0x5555

*SysAddr8 (sysbase, 0x2AAA) = 0x55; //Write the value 0x55 to FLASH address 0x2AAA

*SysAddr8 (sysbase, 0x5555) = 0xA0; //Write the value 0xA0 to FLASH address 0x5555

*SysAddr8(sysbase, addr) = data; //Write a BYTE data to the address when it expires

2.5 16-BIT FLASH programming driver example-SST39VF160

SST39VF160 is a 16-BIT NOR FLASH of SST Company. In this section, we take SST39VF160 as an example to describe how to operate 16-BIT NOR FLASH. The operation of 8-BIT FLASH is well understood, but the operation of 16-BIT FLASH is much more obscure. I tried my best to be clearer.

The capacity of SST39VF160 is 2M-BYTE, including 512 SECTORs in total, and the capacity of each SECTOR is 4K-BYTE. The chip supports SECTOR erase, block erase and write operations with HALF-WORD as the basic unit. SST39VF160 commands The definition is shown in Table-2. In Table 2, all commands are defined from the perspective of FLASH. Therefore, all addresses are HALF-WORD addresses, which refer to the addresses seen by the 16-BIT FLASH on its address signal An-A0.

In the description later in this section, we use the following 2 definitions:

U32 sysbase; //This variable is used to indicate the starting address of FLASH

#define SysAddr16(sysbase, offset) ((volatile U16*)(sysbase)+(offset)) //Used to facilitate operations on the specified FALSH address

SysAddr16 (sysbase, offset) first defines a 16-BIT HALF-WORD pointer, the address of the pointer is sysbase, and then an offset operation is performed according to the offset. Since the address of the HALF-WORD pointer is aligned with 2 BYTEs, each offset manipulation will increase the address by 2. Ultimately, SysAddr16 (sysbase, offset) is equivalent to defining a HALF-WORD pointer, and its ultimate address is ( sysbase + 2offset). When using SysAddr16, set sysbase to the starting address of FLASH, and offset can be understood as the HALF-WORD offset or offset address relative to the starting address of FLASH. Assuming that the starting address of FLASH is 0x10000000, SysAddr16 (0x10000000, 0) points to the 0th HALF-WORD of 16-BIT FLASH, SysAddr16 (0x10000000, 1 points to the first HALF-WORD of 16-BIT FLASH, and so on. Suppose. To write 0xABCD to the 0th and 1st HALF-WORD of FLASH respectively, you can use the following code:

*SysAddr16 (0x10000000, 0x0) = 0xABCD;

*SysAddr16 (0x10000000, 0x1) = 0xABCD;

Next, we will analyze in detail from the angle of the ARM processor and the angle of FLASH.

From ARM's point of view:

Assuming that the starting address of FLASH is 0x10000000, because the ARM processor knows that the address space of FLASH is 0x10000000 ~ (0x10000000 + FLASH capacity-1), so when accessing this address space, the chip select signal of FLASH will be set, And output the low-order address to the address signal. Take *SysAddr16 (0x10000000, 0x1) = 0xABCD as an example. From the ARM processor's point of view, the operation is to write 0xABCD to address 0x10000002. So the ARM processor will eventually output address 0x2 on its address signal An-A0, and at the same time it will output 0xABCD on D15-D0.

From the perspective of FLASH:

Or take *SysAddr16(0x10000000, 0x1) = 0xABCD as an example, what address does FLASH see? Then analyze. When the ARM processor performs the operation, it will set the corresponding FLASH chip select enable signal, and output 0x2 on the ARM address signal An-A0. Because the connection between the ARM and 16-BIT FLASH address signal is Staggered by one bit, so the signal that FLASH finally sees at its address An-A0 is 0x1, which is equivalent to shifting the address output by the ARM processor to the right, which corresponds to the first number of FLASH. A HALF-WORD. At the same time, FLASH will see the data 0xABCD on its D15-D0.

Through the above analysis, we know that the offset value specified in SysAddr16 is the value seen by 16-BIT FLASH on its address An-A0. Therefore, we can easily manipulate FLASH through SysAddr16 (sysbase, offset), where sysbase represents the start address of FLASH, and offset represents the HALF-WORD (HALF-WORD offset or offset address) of FLASH. )

note:

In the description later in this section, SYSBASE in SysAddr16 represents the start address of FLASH, and OFFSET in SysAddr16 represents the HALF-WORD offset or offset address. OFFSET value relative to the start address of FLASH. It is also the value seen by 16-BIT FLASH on its own address signal An-A0;

In the command definition of SST39VF160, all addresses are HALF-WORD addresses for FLASH, referring to the addresses seen on FLASH's own address signal An-A0.

Mass erase operation

The entire chip erase operation requires a total of 6 cycles of bus write operations:

Write 0x00AA to FLASH HALF-WORD address 0x5555;

Write 0x0055 to FLASH HALF-WORD address 0x2AAA;

Write 0x0080 to FLASH HALF-WORD address 0x5555;

Write 0x00AA to FLASH HALF-WORD address 0x5555;

Write 0x0055 to FLASH HALF-WORD address 0x2AAA;

Write 0x0010 to FLASH HALF-WORD address 0x5555.

Corresponding code:

*SysAddr16 (sysbase, 0x5555) = 0x00AA; //Write the value 0x00AA to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x2AAA) = 0x0055; //Write the value 0x0055 to FLASH HALF-WORD address 0x2AAA

*SysAddr16 (sysbase, 0x5555) = 0x0080; //Write the value 0x0080 to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x5555) = 0x00AA; //Write the value 0x00AA to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x2AAA) = 0x0055; //Write the value 0x0055 to FLASH HALF-WORD address 0x2AAA

*SysAddr16 (sysbase, 0x5555) = 0x0010; //Write the value 0x0010 to FLASH HALF-WORD address 0x5555

SECTOR erase operation

The erase operation of SECTOR requires a total of 6 cycles of bus write operations:

Write 0x00AA to FLASH HALF-WORD address 0x5555;

Write 0x0055 to FLASH HALF-WORD address 0x2AAA;

Write 0x0080 to FLASH HALF-WORD address 0x5555;

Write 0x00AA to FLASH HALF-WORD address 0x5555;

Write 0x0055 to FLASH HALF-WORD address 0x2AAA;

Write 0x0030 to the HALF-WORD address corresponding to the SECTOR to be erased.

Corresponding code:

Copy code

*SysAddr16 (sysbase, 0x5555) = 0x00AA; //Write the value 0x00AA to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x2AAA) = 0x0055; //Write the value 0x0055 to FLASH HALF-WORD address 0x2AAA

*SysAddr16 (sysbase, 0x5555) = 0x0080; //Write the value 0x0080 to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x5555) = 0x00AA; //Write the value 0x00AA to FLASH HALF-WORD address 0x5555

*SysAddr16 (sysbase, 0x2AAA) = 0x0055; //Write the value 0x0055 to FLASH HALF-WORD address 0x2AAA

*SysAddr16 (sysbase, addr "" 1) = 0x0030; //Write the value 0x0030 to the HALF-WORD address corresponding to the SECTOR to be erased

Copy code

note:

The ADDR in the 6th operation cycle in the above code is the BYTE address from the perspective of the ARM processor, because when erasing, the user wants to specify the address from the perspective of the ARM, which is more convenient And more intuitive. In the macro definition of SysAddr16, OFFSET represents the HALF-WORD offset relative to the start address of FLASH, or the address that FLASH sees on its address signal An-A0. So you need to perform a right shift operation to convert ADDR into HALF-WORD address.

For example, the size of each SECTOR of SST39VF160 is 4K-BYTE. From the perspective of the ARM processor and the user, the BYTE address of SECTOR-0 relative to the start address of FLASH is 0x0; from the perspective of FLASH, the value of SECTOR-0 is The HALF-WORD address is 0x0. From the perspective of the ARM processor and the user, the BYTE address of FLASH SECTOR-1 relative to the FLASH start address is 0x1000; from the perspective of FLASH, the HALF-WORD address of SECTOR-1 should be (0x1000 》》 1) = 0x800.

If you want to erase SECTOR-0, the sixth instruction of the above code should be:

*SysAddr16 (sysbase, 0x0 "" 1) = 0x0030;

If you want to erase SECTOR-1, the sixth instruction of the above code should be:

*SysAddr16 (sysbase, 0x1000 "" 1) = 0x0030;

HALF-WORD programming operation

Writing a HALF-WORD data to FLASH requires 4 cycles of bus write operation:

Write 0x00AA to FLASH HALF-WORD address 0x5555;

Write 0x0055 to FLASH HALF-WORD address 0x2AAA;

Write 0x00A0 to FLASH HALF-WORD address 0x5555;

Write the programming data (HALF-WORD) to the corresponding HALF-WORD address.

Corresponding code:

*SysAddr16 (sysbase, 0x5555) = 0x00AA; //Write the value 0x00AA to FLASH address 0x5555

*SysAddr16 (sysbase, 0x2AAA) = 0x0055; //Write the value 0x0055 to the FLASH address 0x2AAA

*SysAddr16 (sysbase, 0x5555) = 0x00A0; //Write the value 0x00A0 to the FLASH address 0x5555

*SysAddr16 (sysbase, addr "" 1) = data; //Write the data to the corresponding HALF-WORD address

note:

The ADDR in the 4th operation cycle of the above code is the BYTE address from the perspective of the ARM processor, because when the write operation is performed, the user wishes to specify the address from the perspective of the ARM More convenient and more intuitive. In the macro definition of SysAddr16, OFFSET represents the HALF-WORD offset relative to the start address of FLASH. So you need to perform a right shift operation to convert it into a HALF-WORD address.

For example, to write data 0x0123 to address 0x0, which corresponds to the 0th HAFL-WORD of FLASH, the corresponding HALF-WORD address should be 0x0, and the fourth instruction of the above code should be:

*SysAddr16 (sysbase, 0x0 "" 1) = 0x0123;

Another example is to write data 0x4567 to address 0x2, which corresponds to the first HALF-WORD of FLASH, and the corresponding HALF-WORD address should be 0x1. The fourth instruction of the above code should be:

*SysAddr16 (sysbase, 0x2 "" 1) = 0x4567;

Another example is to write data 0x89AB to address 0x4, which corresponds to the second HALF-WORD of FLASH, and the corresponding HALF-WORD address should be 0x2. The fourth instruction of the above code should be:

*SysAddr16 (sysbase, 0x4 "" 1) = 0x89AB;

If you want to write data 0xCDEF to address 0x6, it corresponds to the third HALF-WORD of FLASH, and the corresponding HALF-WORD address should be 0x3. The fourth instruction of the above code should be:

*SysAddr16 (sysbase, 0x6 "" 1) = 0xCDEF;

2.6 Summary

The above briefly introduces the principle of NOR FLASH and how to operate NOR FLASH, but does not include other operations such as status query and protection. There is no discussion about the more complicated multi-chip FLASH parallel connection, if you need it, you can analyze it yourself.

ConclusionThis is the end of the related introduction about norflash. Please correct me if there are any deficiencies.

Related reading recommendations: Detailed explanation of the difference between NAND flash and NOR flash

Related reading recommendations: NOR FLASH: Analysis of the principle and application of large-capacity memory chips

51V Battery Pack,Portable Battery Box,Portable Battery Bank,Ac Battery Pack

Zhejiang Casnovo Materials Co., Ltd. , https://www.casnovonewenergy.com