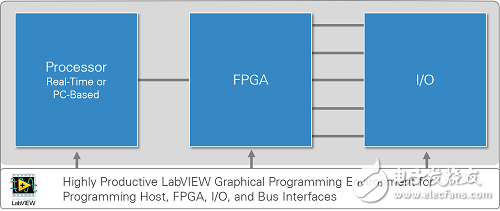

NI R Series multifunction RIO devices feature user-defined onboard processing for maximum system timing and triggering. The R Series hardware uses a user-programmable FPGA to replace the fixed ASIC chip used to control device functionality, allowing all analog and digital I/O channels to be configured for specific applications. With the LabVIEW FPGA Module, you can use LabVIEW control hardware to implement intelligent data acquisition, closed-loop control, digital communication protocols, sensor emulation, and inline signal processing without having to delve into the hardware description language.

LabVIEW RIO Architecture

For more than a decade, engineers and scientists have used R-Series devices and LabVIEW reconfigurable I/O architectures to enhance the functionality of PC-based electronic systems to achieve the performance, stability, and determinism required for their applications. This white paper introduces the R Series devices in the PXIe bus digital I/O class, the latest high-performance technology in the R-series family for custom digital applications.

2. Kintex-7 improves performance and functionality

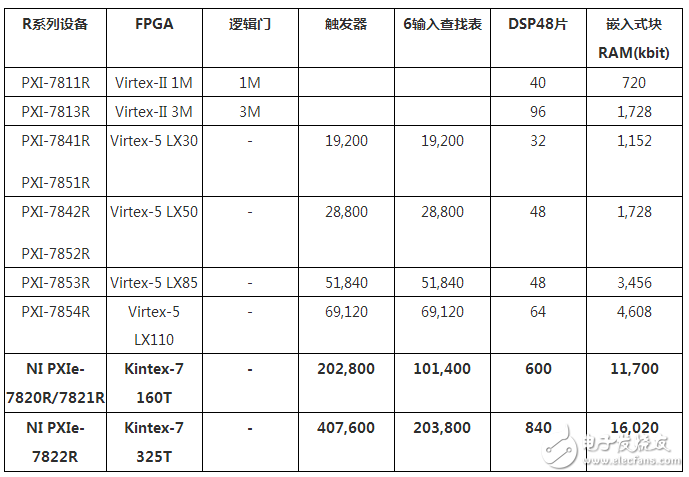

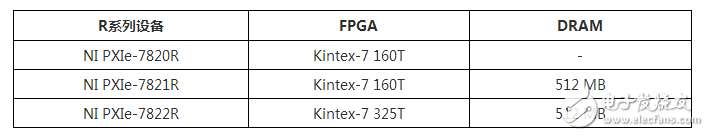

Xilinx's Kintex-7 FPGAs have the same resource capacity and performance as previous generation high-end FPGAs, but consume only half the power of previous generation high-end FPGA chips, making them ideal for R-series devices in the PXIe-bus digital I/O class. The significant reduction in power consumption compared to previous generation digital I/O class R Series devices allows each device to allocate more digital signal processing (DSP) resources. As logical and DSP resources increase, you can use more extensive signal processing techniques and real-time analytics to implement more complex algorithms that address the growing I/O data rates and the complexity of today's applications. . Table 1 compares the FPGA used in the PXIe bus digital I/O class R series devices with the FPGAs used in the previous generation PXI bus R series devices.

Table 1. FPGA Comparison in PXI and PXIe Bus R Series Devices

3. New featuresThe PXIe bus digital I/O class R series devices have some new features that are superior to the PXI bus R series devices. These features include user selectable logic levels, faster digital I/O rates, DRAM options, higher data streaming capability, and external clock input.

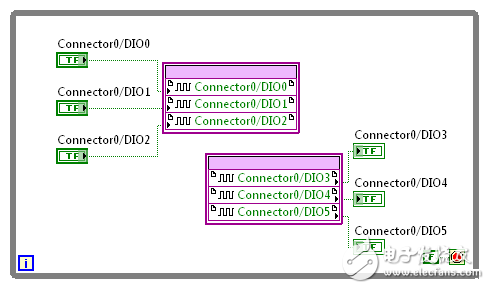

R Series devices use a programmable FPGA to replace fixed-function ASIC chips to control device functionality, so you can configure I/O to meet your specific application needs. With LabVIEW FPGA, a single piece of hardware can meet the most demanding requirements and can be easily reconfigured to meet future application needs. The example in Figure 3 shows how to use LabVIEW FPGA programming to continuously read and write data on the digital I/O lines of R Series devices.

Simple DIO functionality with R Series devices

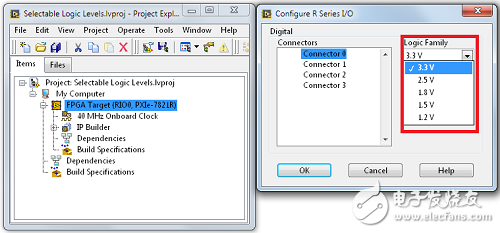

Optional digital logic level

The flexibility of R Series devices enables the implementation of critical applications such as communication with custom digital protocols. For example, you can put the protocol codec part on the FPGA of the R series device to reduce the processing load of your host computer and simplify the host computer program, so that the host computer program can directly use the data to work without touching the underlying protocol signal. Another example is protocol communication with certain devices that need to respond to specific signals over a fixed time frame. FPGAs process specific data through onboard resources without passing data back and forth between the FPGA and the CPU. The FPGA reduces latency and gives you the ability to implement the requirements mentioned in the second example. However, not all devices under test (DUTs) have the same communication logic level. The programmable digital logic level allows you to connect directly to the DUT when using PXIe bus digital I/O class R series devices. The programmable digital logic levels include: 3.3V, 2.5V, 1.8V. , 1.5V and 1.2V.

PXIe bus digital I/O class R series devices provide selectable digital logic levels

Faster DIO Rates In addition to the choice of digital logic levels, PXIe digital I/O class R Series devices offer faster DIO rates than previous generation devices. The maximum frequency supported by DIO on these new devices is up to 80MHz.

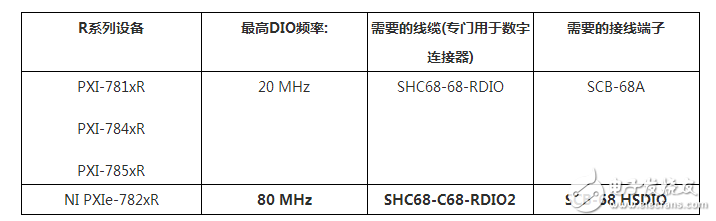

Table 2. Maximum DIO Frequency and Required Accessories for PXI and PXIe Digital I/O Class R Series Devices

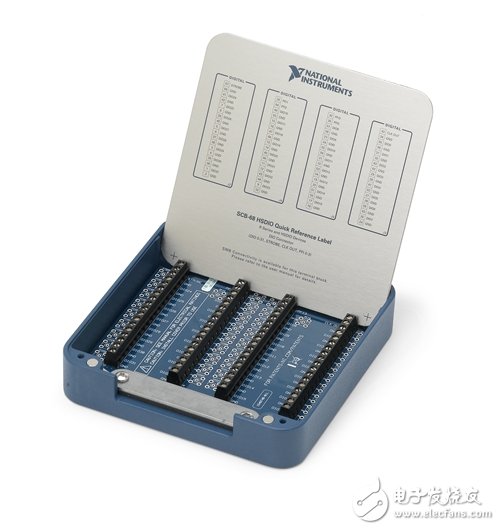

To support higher speeds, NI designed new cable and junction box accessories. The PXIe Digital I/O Class R Series devices use the SHC68-C68-RDIO2 cable and the SCB-68 HSDIO junction box to replace the SHC68-68-RDIO cable and the SCB-68A junction box used in previous generation devices.

PXIe Digital I/O Class R Series devices support high performance signals with high performance accessories

These accessories provide an impedance matching connection between the FPGA and the DUT, which allows the R Series devices to operate at higher rates while also providing high signal integrity.

DRAM

Many high performance instruments use DRAM as a local storage. PXIe Digital I/O Class R Series devices provide DRAM resources so you can completely freely integrate this form of local storage resources into your own applications. Typical DRAM uses include providing simple local storage for record-based acquisition/generation applications, and implementing long delay chains for channel emulation.

Table 3. PXIe R Series DRAM Options

Data Streaming Many applications need to stream data from one place to another. Such a data stream disk can be between the host CPU and a single hardware module, or it can be from one module to another without going through the host at all. The data stream between the first host and the FPGA on the R Series device is implemented by a DMA FIFO that allows the FPGA to use the host's RAM to transfer data between the FPGAs as if it were its own. The previous generation R Series devices had three DMA FIFOs, which could be used independently in a single direction. With the new family members of the PXIe-782x R Series, you have access to 16 separate DMA channels that you can use to transfer data from the terminal to the host or from the host to the terminal.

The second type of stream is a module-to-module method that does not pass through the host at all. This process is known as a peer-to-peer (P2P) data stream. NI P2P data stream technology uses the PCIe bus to allow direct point-to-point data transfer between multiple instruments without going through the host processor or memory. This technology allows information to be shared between devices in a system without burdening other system resources. In addition to PXIe bus digital I / O class R series devices, PXIe bus FlexRIO module also supports NI P2P technology, PXIe bus digitizer, vector signal analyzer, vector signal generator and arbitrary waveform generator also support NI P2P technology . To learn more about P2P streaming, please visit the peer-to-peer data flow.

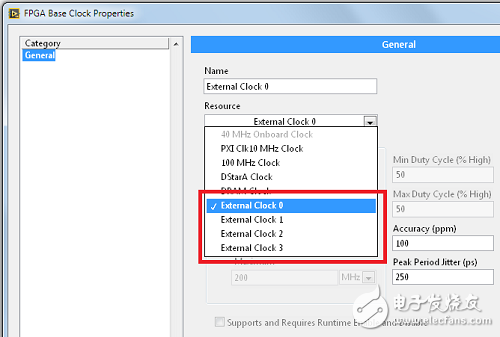

External Clocks When programming with previous generation R Series devices, you have to use a 40MHz time base or derive a clock from the time base. The time base is a digital signal in hardware that can be used as a clock for FPGA applications. The derived clock is a clock created by the time base. You can also use the derived clock as the clock for the FPGA application. The time base and derived clocks help you specify the execution rate of a single-cycle Timed Loop. However, when you create a derivative clock in a LabVIEW project, LabVIEW looks for a frequency that is actually supported by the FPGA and is closest to the target frequency as the frequency of the derived clock. Such a frequency may not meet the needs of your particular application. In the PXIe bus's digital I/O class R Series devices, you can import up to four external stable clock sources into LabVIEW and drive your DIO at these specified clock rates, each of the four external clock sources. The maximum supported frequency is up to 80MHz.

Digital I/O Class R Series devices on the PXIe bus allow you to import external reference clocks up to 80MHz

4. Other resourcesBrowse the digital I/O class R series products of PXIe bus

View R Series equipment, product overview, strengths, and technical resources

Learn more about programming R-Series devices in LabVIEW

Priva PF series Rental led display are specally designed for stage or event show which need fast installation and disamantle. One cabinet type could be used for indoor and outdoor enviroment. It also has option for curve. Advanced high brightness with high gray scale technology, high contrast ratio, excellent refresh ratio, and all these features guarantees a brilliant and beautiful Rental LED screen

Along with the LED encapsulation technology and SMT production line developed , the outdoor small pixel pitch LED display screens or High definion led display for rental get popular.Stage LED display are designed for stage or shows. Nowadays, more and more shows and events are equipped with rental LED screen for video displaying or stage background. Due to its unfixed usage occasion, Stage LED display are requested to be easy assemble and disassemble.

Rental Led Display ,Rental Led Screen, Stage Led Display, Stage led screen

Shenzhen Priva Tech Co., Ltd. , https://www.privaled.com