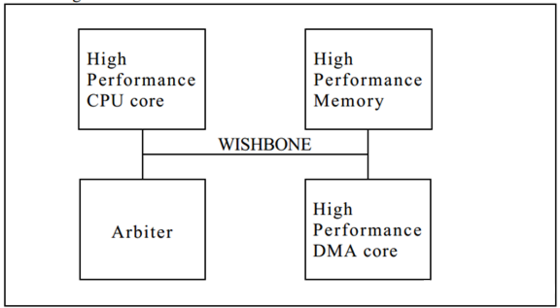

Wishbone bus is an on-chip bus protocol launched by Silicore. Its structure is extremely simple, flexible, and completely open, completely free, and it has a lot of support. Figure 3 shows the logical structure of the Wishbone bus: The main features of the Wishbone bus are summarized as follows:

Figure 29 Wishbone bus structure diagram

â— All applications use a bus architecture; â— Simple and compact architecture; â— Support multiple controllers; â— 64-bit address space; â— 8-64-bit data bus (expandable); â— Single-cycle read and write; â— RMW (READ-MODIFY-WRITE) cycle; â— Event cycle; â— Support retry; â— Support memory mapping, FIFO (FISRT IN FIRST OUT) and cross interconnect interface; â— Provide a mechanism to throttle data flow for slower device use; â— The user-defined flag is to determine the data transmission type; â— The arbitration method is defined by the end user.

to sum up

Among the three buses introduced above, CoreConnect is free but requires a license from IBM. ARM does not have a clear official statement and may also be free, while Wishbone is absolutely free. The three kinds of buses are synchronous buses, and use the rising edge of the clock to drive the 8-bit SLAVE output port and sample the signal. There is almost no difference in the basic operation of the bus. The biggest difference lies in the integrity of the features and specifications provided. Both CoreConnect and AMBA provide designers with a choice of system bus. System integration designers will encounter problems when trying to connect devices designed for different connections, and bridges are needed to build a comprehensive system. In Wishbone, all IP cores are connected to the same standard interface. System designers can choose to implement two interfaces on a microprocessor core, one for high-speed and low-latency devices, and one for low-speed and low-performance devices. In summary, we believe that it is more convenient to design the interface standard for the basic interconnection of the IP core using Wishbone. Its signal is very direct and can be easily adopted by other interfaces if necessary.

The Wishbone bus is completely open, completely free, and easy to promote. Of course, whether a specification can become an industry standard depends on whether it is accepted by the industry in addition to its own technical characteristics. Wishbone has been adopted by the OPENCORE alliance and may become an IEEE standard. Therefore, the Wishbone bus is technically simple, flexible, powerful and easy to transplant, and it is all free from an economic point of view, and it is easy to promote in an all-round way. We think it is very likely to become the general standard of SoC on-chip buses in the future, and its prospects are promising.

Mid-Range Frequency Loudspeaker

NINGBO LOUD&CLEAR ELECTRONICS CO.,LIMITED , https://www.loudclearaudio.com