The world is crazy, it seems that someone started learning FPGAs without even knowing the FPGA principle.

DSP is a processor with a unique instruction. Although it is a general purpose processor, it is actually not "universal". A very skilled person can use DSP to make a computer and run out of windows, but in fact it is definitely a fool. Signal processing with DSP is more powerful than other types of processors; things other than signal processing with DSP are not long. And the code processing code generally needs to be well written by people who are proficient in the algorithm.

The time complexity and space complexity in the data structure is a very harsh ruler here. The FPGA is just a cloak of software, actually hardware. There are two layers of relatively independent circuits inside the FPGA. The user "codes -> compiles" to generate an image that acts on the first layer of circuitry. This layer of circuit is a 0,1 switch matrix, this switch matrix is ​​used to control the second layer of working circuit, the second layer of working circuit is configured as a corresponding processor.

In theory, the FPGA can be configured to any processor that is needed. In fact, in order to minimize bugs, FPGA development uses the already developed "library files", which is to take the circuit diagrams that people can work stably.

Therefore, for most FPGA developers, there are several cores inside the FPGA that can only be selected from the library file - unless you have the ability to design the core internal circuit and the inter-core bus - ram and rom are also used To configure, you only need to change the external dedicated circuit and wiring method.

Even external dedicated circuits have library files, and building blocks is complete. The person who really plays the money in FPGA is the person who builds the building blocks. If you create a few building blocks and can apply for a patent, forcing others to pay you a patent fee, then you can eat and worry in this life.

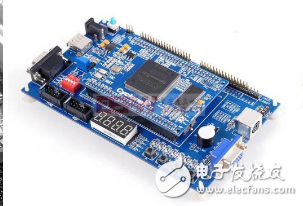

FPGA is different from ASIC design. It belongs to the category of hardware design. ASIC is hardware. Fully custom FPGA is hardware semi-custom. Specifically, the whole circuit of ASIC is designed by designers. How much resources are used to design how much resources are generally used for product design. FPGA resources are Given by vendors, such as Altera Xilinx, which provide different series of FPGA chips, designers can do hardware design development under given resources.

DSP is mainly used to process signals, prior algorithm, characterized by multi-level pipeline, which can speed up data processing. The development environment is mainly C language. It can be said that the scope of DSP application is more specialized in DSP design. It can be understood as software design, designer. Do not need to understand the structure of the DSP too much.

Add a few small concepts

DSP is willing to refer to digital signal processing, but the DSP chip is abbreviated as DSP (digital signal processor) because its main function is to implement digital signal processing to implement various algorithms.

FPGA can do DSP (digital signal processing), which means that FPGA can be used as hardware design to realize the function of DSP chip. Of course, the cost of professional DSP chip is too high.

In addition to FPGA and DSP, there is a popular product in recent years. ARM. ARM main application and handheld devices and embedded products almost cover 90% of the market share. It can be said that ARM development is also biased towards software development, designers Mainly about the wince system or linux system transplanted to the ARM development platform, and then do a variety of software application development.

So these three directions have different applications, it is difficult to say who is more promising, but, as I personally, I prefer to do hardware design, so I chose FPGA as my own direction FPGA.

Mainly to provide designers with a core of hardware platform development or independent application design and efficient algorithm design, so designers should handle the difference between the master of the tool and the specific design FPGA: parallel processing, internal resources, multiple DSP: low cost , low power consumption, high performance processing capability. A powerful external communication interface (SCI, SPI, CAN) facilitates the construction of a large control system.

Features:

(1) One multiplication and one addition can be completed in one instruction cycle;

(2) The program and the data space are separated, and the instructions and data can be accessed simultaneously;

(3) There is a fast RAM on the chip, which can usually be accessed simultaneously in two blocks through a separate data bus;

(4) Hardware support with low overhead or no overhead loops and jumps;

(5) Fast interrupt handling and hardware I/O support;

(6) having a plurality of hardware address generators operating in a single cycle;

(7) Multiple operations can be performed in parallel;

(8) Support pipeline operations, so that operations such as fetching, decoding, and execution can be performed in an overlapping manner.

I think that FPGA is more promising. DSP is just a special processor. There is a dedicated hardware multiplier. There is a barrel shifter that can move data from memory to ALU, as well as pipelines.

But FPGAs can also do these functions, and FPGAs work in parallel. Now many FPGAs can use soft DSP or hard core DSP. When your project needs strict timing, it is not FPGA.

For example, when using FIFO (synchronous transfer) data with DSP and USB chip CY68013, IFCLK can be external or internal, and the USB chip is configured in IFCLKSRC of IFCONFIG. If the IFCLK is used internally, the DSP can't know how many cycles the USB chip's internal clock has passed after I send the data to the FIFO data port, but the FPGA can do it because the FPGA clock is taken from the 48M output of the USB chip. Internally, a state machine is used. When the data is sent to the FIFO data port of the USB chip, the next state pulls SLWR low, and then the next state is pulled high, which is equivalent to a cycle inside the USB, and the data is written into the USB chip. FIFO, I just give a simple example, many cases of timing are not FPGA, DSP algorithm is fast, mature, FPGA is more challenging, according to my experience, FPGA now has at least a lot of cores available. This is like a configurable microcontroller, I will not put it into the project if I don't need it. For the ACTEL FPGA, the more soft cores used are: Core8051S, CoreABC, and microprocessor soft core. In particular, CoreABC takes up very little space and can cut instructions. The data width can be configured to be 8,16,32. A set of general purpose input and output ports for configurable stacking.

CoreDES, CoreAES128, CoreFROM, CoreI2C, CoreGPIO, CoreInterrupt, CoreLPC, CoreSDR, CoreUART, and many more, look at these names, many people know what to do. What do you think about DPS, FPGA, AME? Which is your favorite?

I/O Connector,Dvi Connector,Rj11 Connector,Iee1394 Connector

Shenzhen Hongyian Electronics Co., Ltd. , https://www.hongyiancon.com